## FEM-IB debugging NWU, NCU, INTT group M1 Mika Shibata 2020/08/07

# table of contents

- 1. Back ground and goal

- 2. What we know about FEM-IB status

- Differences of attached modules

- LED

- Details: LED's color

- Details: LEDs' positions and meanings

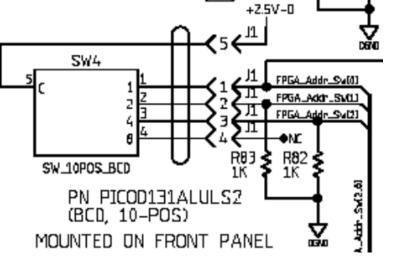

- We made FPGA ADDR switch.

- 3. FPHX chip's current: Data from PC to ROC

- Data from PC to USB port on FEM-IB

- Data from SC port on FEM to ROC

- 4. Summary

# Back ground

• One FEM-IB couldn't work.

## Goal

• Search the cause of this problem and fix it.

## What we know about FEM-IB status Operation status

FEM-IB test

Here is the FEM-IB cheking affair

• We couldn't get data.

Usable cod

FEM-IB cod File name: 3 Download p

- All modules without FEM-IB can work. (cables, INTT, FEM, ROC,…)

- FPGA code of bad FEM-IB is same as that of NWU's.

| for test bench                      | F | FEM IB 1, FEM IB 1 code |                |        |                        |          |     | ROC F<br>ROC cl<br>LV pov<br>FPGA c | : <b>C-1</b><br>: J1A<br>: 3.6V<br>: 0.62A->0.62A              |                           |

|-------------------------------------|---|-------------------------|----------------|--------|------------------------|----------|-----|-------------------------------------|----------------------------------------------------------------|---------------------------|

| -Aug-13<br>ge: Location of the code |   | FEM                     | FEM code       | FEM IB | FEM IB code            | computer | ROC | bco/start board                     | JTAG all cables                                                | result                    |

|                                     | 3 | NWU                     | NWU            | NCU 1  | NCU 1<br>(same as NWU) | NWU      | NWU | NWU                                 | NWU                                                            | bad                       |

|                                     |   | No da                   | ld             |        |                        |          |     | ROC F                               | PGA and port                                                   | · C-3                     |

|                                     |   |                         |                |        |                        |          |     | ROC cl<br>LV pov<br>FPGA (          | PGA and port<br>hip power cable port<br>ver setting<br>current | : 3.61V<br>: 0.66A->0.66A |

|                                     |   | FEM                     | Ld<br>FEM code | FEM IB | FEM IB code            | computer | ROC | ROC cl<br>LV pov                    | hip power cable port<br>ver setting                            | : J2A<br>: 3.61V          |

## What we know about FEM-IB status

- 1. Differences of attached modules

- 2. Slow Control can work.

- FEM-IB's LED can change when we sent command via GUI.

- 3. FPHX chip's current doesn't change.

Numbers which are written on FEM board panel are different from numbers of FPGA codes!

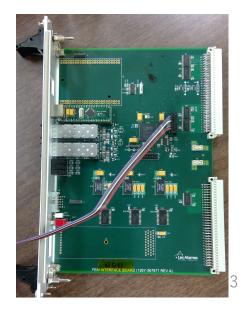

## What we know about FEM-IB status Differences of attached modules

## good FEM IB (box6)

#### Things not attached

(In the test at NWU, we used NWU's receiver to connect optical cable.)

Start receiver

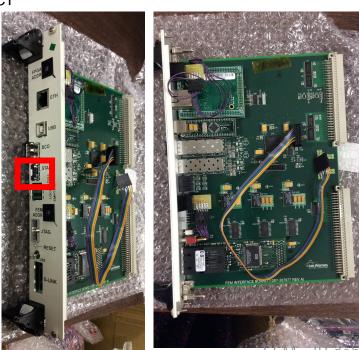

# *bad* FEM IB 1

Things not attached

These modules are not used for Test Bench.

(In the test at NWU, we didn't use any NWU's things for below places.)

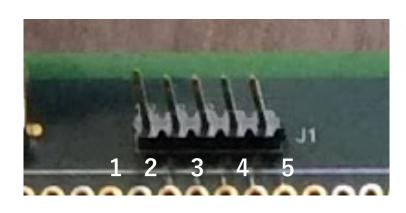

- FPGA ADDR

- ETH

- ROC ADDR

- G-LINK

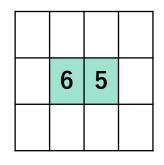

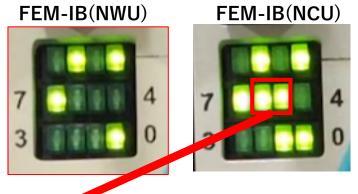

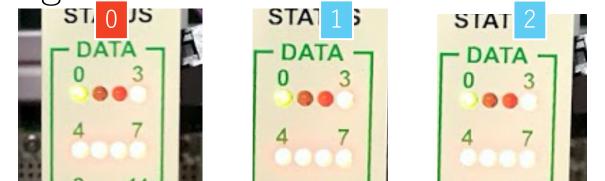

# What we know about FEM-IB status LED

• No.5, 6 are lighting while the FEM-IB power is on.

$\rightarrow$ The problem may come from the lack of modules. (No.5, 6 LED show "CRATE\_ID")

# FPGA ADDR ETH ROC ADDR G-LINK

LOCKED <= LOCKED\_int; LED\_OUT(7) <= not GTM\_LINK; --LED\_OUT(6) <= GLINK\_RST\_int; LED\_OUT(6 downto 5) <= CRATE\_ID; --LED\_OUT(4) will go on if a start\_calib command received from GTM LED\_OUT(3 downto 0) <= COMMAND\_VME\_int(3 downto 0);

FEM\_IB\_top.vhd

#### The FEM-IB's LED can move same as good FEM-IB's.

<del>2020/8/7</del>

# Detail: LED's color

- LED TEST[] (1 downto 0)

- LED OUT(0)=0 : RED

- LED\_OUT(0)=1 : Green

- LED OUT(0)=Z : none

- LED  $OUT() \le 0'$  and '1' mean that the LED's color is red and green respectively.  $LED_OUT() \le 'Z'$  means that the LED isn't turn on.

- LED\_TEST(0)=0(both NCU and NWU)

- LED\_TEST(1)=0(both NCU and NWU)

```

LED OUT(3) \ll LED_TEST(0) when LED_TEST(1) = '1' else

'Z' when (LED_TEST(1) = '0' \text{ and } LED_TEST(0) = '1') else

'1' when EMPT\overline{Y} = '1' else

'Z';

LED OUT(2) \ll LED TEST(0) when LED TEST(1) = '1' else

'Z' when (LED TEST(1) = '0' and LED TEST(0) = '1') else

'0' when BUSY = '1' else

'Z';

LED_OUT(1) \ll LED_TEST(0) when LED_TEST(1) = '1' else

'Z' when (LED_TEST(1) = '0' \text{ and } LED_TEST(0) = '1') else

'0' when MODE = '1' else

'Z';

LED OUT(0) \ll LED TEST(0) when LED TEST(1) = '1' else

'Z' when (LED_TEST(1) = '0' and LED_TEST(0) = '1') else

'Z'; ---'0' when MODE 2 = '1' else 'Z'; --LOCKED int = '1' else 'Z';

```

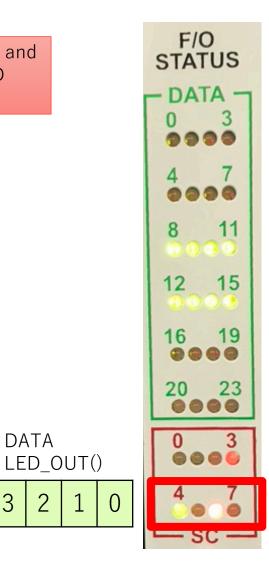

DATA

2

3

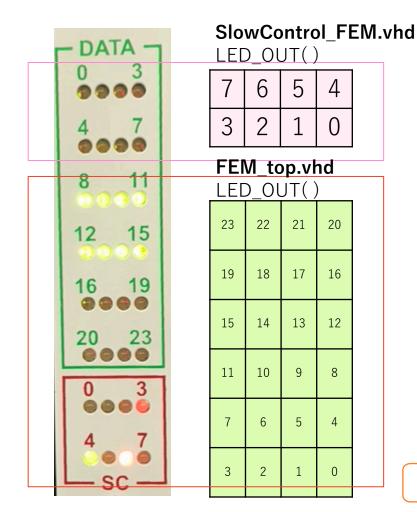

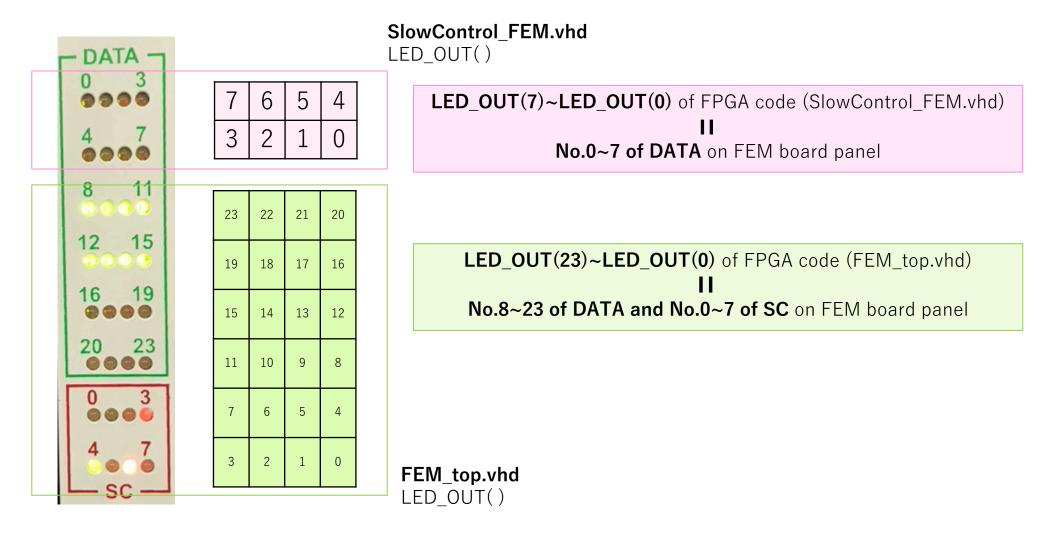

# Detail: FEM LED position and the meaning

Numbers which are written on FEM board panel are **different** from numbers of FPGA codes.

| LED_OUT(7)~LED_OUT(0) of FPGA code (SlowControl_FEM.vhd) | LED_OUT(23)~LED_OUT(0) of FPGA code (FEM_top.vhd)   |

|----------------------------------------------------------|-----------------------------------------------------|

| II                                                       | II                                                  |

| No.0~7 of DATA on FEM board panel                        | No.8~23 of DATA and No.0~7 of SC on FEM board panel |

| SYNC_OK          | COMMAND_VME(2) = '1' | COMMAND_VME(1) = '1' | COMMAND_VME(0) = '1' |

|------------------|----------------------|----------------------|----------------------|

|                  | and ((FEM_ADDR_VME = | and ((FEM_ADDR_VME = | and ((FEM_ADDR_VME = |

|                  | FEM_ADDR_REF) or     | FEM_ADDR_REF) or     | FEM_ADDR_REF) or     |

|                  | FEM_ADDR_VME = x"F") | FEM_ADDR_VME = x"F") | FEM_ADDR_VME = x"F") |

| FEM_LVL1_DELAY(3 | FEM_LVL1_DELAY(3     | FEM_LVL1_DELAY(3     | FEM_COMB_MODE        |

| downto 1)        | downto 1)            | downto 1)            |                      |

| ENPTY            | BUSY             | MODE             | Z                |

|------------------|------------------|------------------|------------------|

| DATA_IN_0_BUF(0) | DATA_IN_1_BUF(0) | DATA_IN_2_BUF(0) | DATA_IN_3_BUF(0) |

| SYNC_OK_0_3      | SYNC_OK_0_2      | SYNC_OK_0_1      | SYNC_OK_0_0      |

| SYNC_OK_1_3      | SYNC_OK_1_2      | SYNC_OK_1_1      | SYNC_OK_1_0      |

| SYNC_OK_2_3      | SYNC_OK_2_2      | SYNC_OK_2_1      | SYNC_OK_2_0      |

| SYNC_OK_3_3      | SYNC_OK_3_2      | SYNC_OK_3_1      | SYNC_OK_3_0      |

**ENPTY and BUSY flash when calibration test is running**

# Detail: FEM LED position and the meaning

Numbers which are written on FEM board panel are **different** from numbers of FPGA codes.

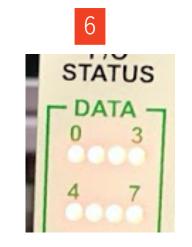

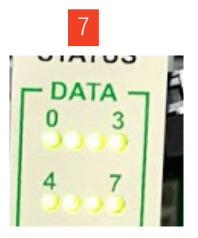

## Detail: SC LEDs of FEM

#### SC LEDs can change according to input signal (FPGA\_ADDR\_VME (2 downto 0)) from FPGA ADDR on FEM-IB board.

- Bad FEM-IB doesn't have FPGA ADDR module so the signal shows "000".

- Good FEM-IB have FPGA ADDR module so the signal can change.

- These LED's are correctly working. (we checked FPGA code (FEM\_IB\_top.vhd))

| FPGA<br>ADDR | FPGA_ADDR_VME<br>(2 downto 0) | Calibration test<br>result |        |           |        |        |

|--------------|-------------------------------|----------------------------|--------|-----------|--------|--------|

| 0            | 000                           | OK                         |        | 0 3       | 0 3    | 0 3    |

| 1            | 001                           | failed                     | 4 7    | 4 7       | 4 7    | 4 7    |

| 2            | 010                           | failed                     |        | 0000      | 0000   | - eeee |

| 3            | 011                           | OK                         | STATUS | STATUS    | STATUS | SIAID  |

| 4            | 100                           | failed                     |        | CDATA - 5 | DATA - | - DATA |

| 5            | 101                           | OK                         |        | 0000      | 0 3    | 0 3    |

| 6            | 110                           | OK                         | 4 7    | 4 7       | 4 7    | 1 7    |

| 7            | 111                           | OK                         |        | 0000      | eeee   | 1 3000 |

2020/8/7

## Detail: FEM LED meaning check

LED\_OUT(7) <= '1' when SYNC\_OK = '1' LED\_OUT(6) <= '0' when COMMAND\_VME(2) = '1' and ((FEM\_ADDR\_VME = FEM\_ADDR\_REF) or FEM\_ADDR\_VME = x"F") else 'Z'; LED\_OUT(5) <= '0' when COMMAND\_VME(1) = '1' and ((FEM\_ADDR\_VME = FEM\_ADDR\_REF) or FEM\_ADDR\_VME = x"F") else 'Z'; LED\_OUT(4) <= '0' when COMMAND\_VME(0) = '1' and ((FEM\_ADDR\_VME = FEM\_ADDR\_REF) or FEM\_ADDR\_VME = x"F") else 'Z'; LED\_OUT(3 downto 1) <= FEM\_LVL1\_DELAY(3 downto 1); LED\_OUT(0) <= '0' when FEM\_COMB\_MODE = '1'

- SYNC\_OK = '1' GREEN

- COMMAND\_VME(0) = '1' **none"Z**"

- COMMAND\_VME(1) = '1' **none"Z**"

- COMMAND\_VME(2) = '0' **RED**

- FEM\_LVL1\_DELAY(3 downto 1) = "000" **RED RED RED**

- FEM\_COMB\_MODE = '1' **RED**

STATU

SIAIUS

# Detail: FEM LED meaning check

LED\_OUT(0) <= FPGA\_ADDR\_VME(0) when FPGA\_ADDR\_VME(2 downto 1) = "11" LED\_OUT(3 downto 1) <= "111" when FPGA\_ADDR\_VME = "111" else "000" when FPGA\_ADDR\_VME = "110" LED\_OUT(4) <= FPGA\_ADDR\_VME(0) when FPGA\_ADDR\_VME(2 downto 1) = "11" LED\_OUT(5) <= FPGA\_ADDR\_VME(0) when FPGA\_ADDR\_VME(2 downto 1) = "11" LED\_OUT(6) <= FPGA\_ADDR\_VME(0) when FPGA\_ADDR\_VME(2 downto 1) = "11" LED\_OUT(7) <= FPGA\_ADDR\_VME(0) when FPGA\_ADDR\_VME(2 downto 1) = "11"

6. FPGA\_ADDR\_VME(2 downto 0) = "110"  $\rightarrow$  FPGA\_ADDR\_VME(0) = 0->Red

7. FPGA\_ADDR\_VME(2 downto 0) = "111" → FPGA\_ADDR\_VME(0) = 1->Green

$$\begin{split} \mathsf{LED}_\mathsf{OUT}(0) &<= \mathsf{'Z' when FPGA}_\mathsf{ADDR}_\mathsf{VME} = \mathsf{"101"}\\ \mathsf{LED}_\mathsf{OUT}(3 \text{ downto } 1) &<= \mathsf{"ZZZ" when FPGA}_\mathsf{ADDR}_\mathsf{VME} = \mathsf{"101"}\\ \mathsf{LED}_\mathsf{OUT}(4) &<= \mathsf{'Z' when FPGA}_\mathsf{ADDR}_\mathsf{VME} = \mathsf{"101"}\\ \mathsf{LED}_\mathsf{OUT}(5) &<= \mathsf{'Z' when FPGA}_\mathsf{ADDR}_\mathsf{VME} = \mathsf{"101"}\\ \mathsf{LED}_\mathsf{OUT}(6) &<= \mathsf{'Z' when FPGA}_\mathsf{ADDR}_\mathsf{VME} = \mathsf{"101"}\\ \mathsf{LED}_\mathsf{OUT}(7) &<= \mathsf{'Z' when FPGA}_\mathsf{ADDR}_\mathsf{VME} = \mathsf{"101"} \end{split}$$

5. FPGA\_ADDR\_VME(2 downto 0) = "101"  $\rightarrow$  FPGA\_ADDR\_VME(0) = 0 -> Z

# We made FPGA ADDR switch

- Bad FEM-IB didn't have this switch so we made it.

- This switch can work expectedly. (This can change FEM's LEDs.)

- But this switch isn't the cause of FEM-IB problem.

# FPHX chip's current doesn't change.

## 1. FPHX chip's current doesn't change.

- The current should decline when "INIT" command is sent. (ex. 0.62A->0.52A)

- On GUI, we checked whether "INIT" command was sent or not and know the command was sent. (Other commands also look workable)

- "FFR" command reaches at ROC board. (The signal can checked on ROC board using oscilloscope)

- FEM-IB USB port can get data correctly.

- We compared these signals of good fem-ib and bad fem-ib.

- These signals are same.

#### Order for global start / Calibration test

- 1. FO Sync

- 2. FPGA RST

- 3. FFR

- 4. Init

- 5. Enable RO

- 6. Latch FPGA

- 7. Set L1 Delay

- 8. BCO Start

- 9. Calib

#### 10.Start\_DAQ

#### "INIT"

: Download parameters to FPHX chips. This needs to be issued after FFR. If INIT has worked properly, you should see the digital current draw for the wedges drop from the value that you have after a FFR.

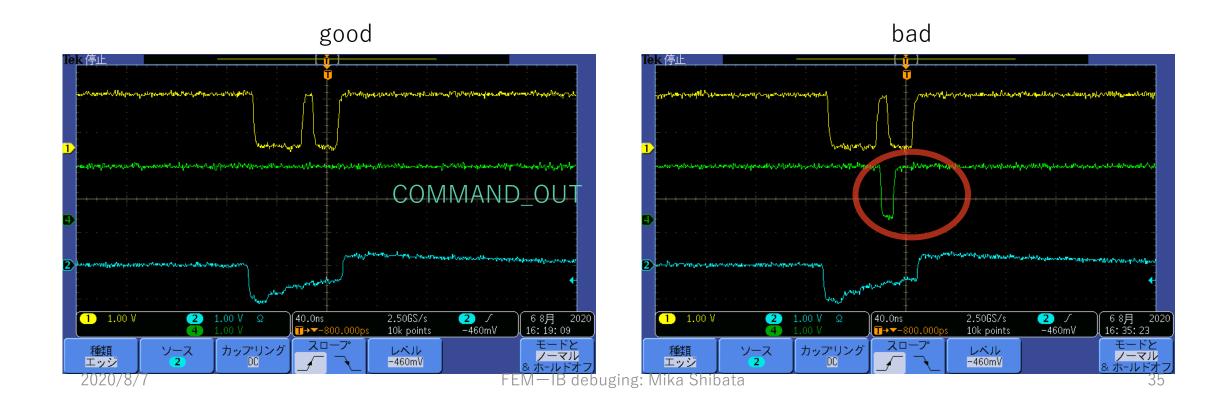

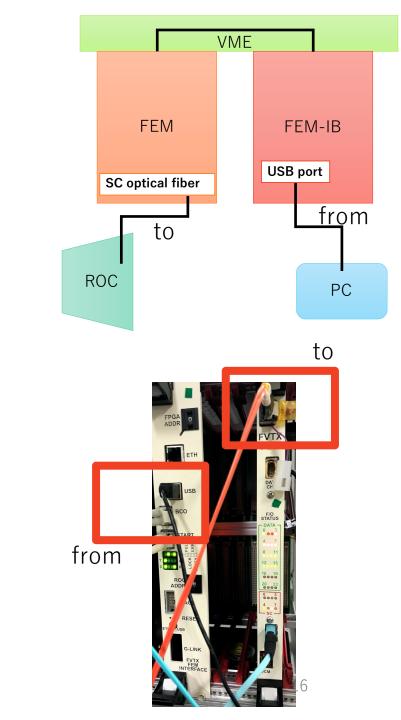

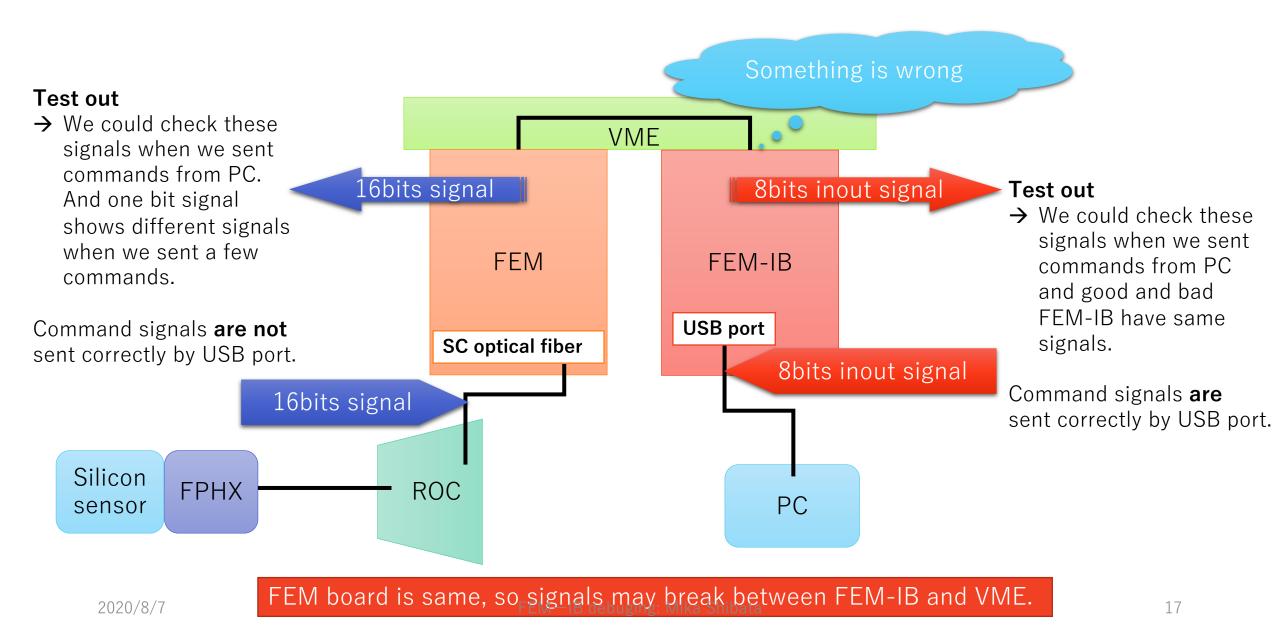

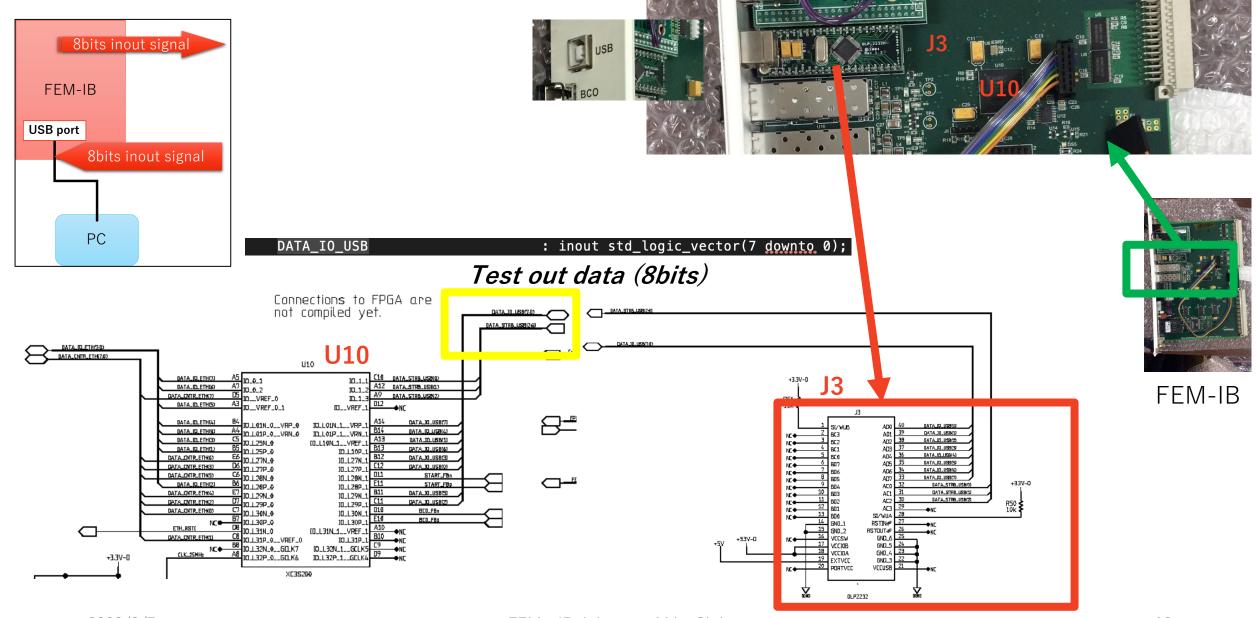

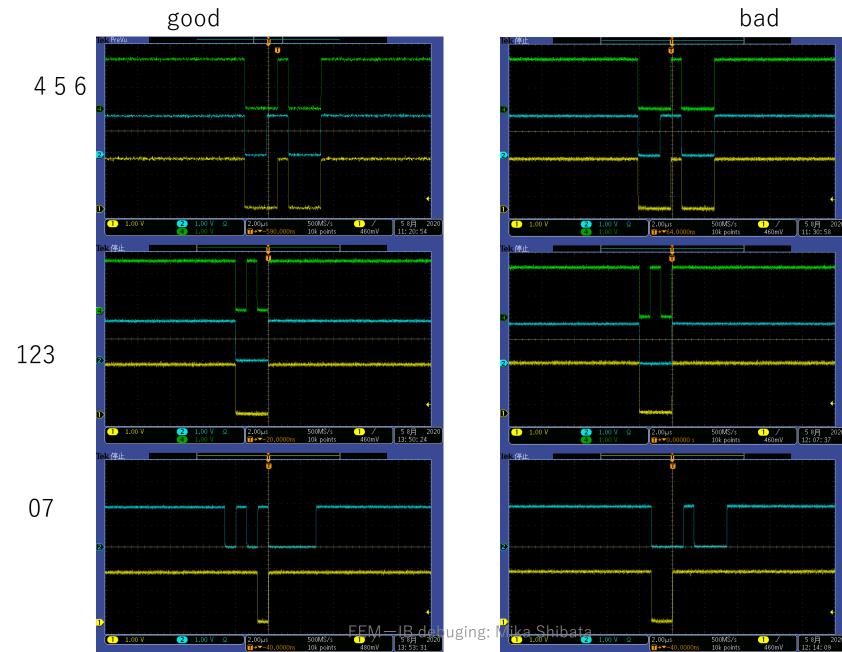

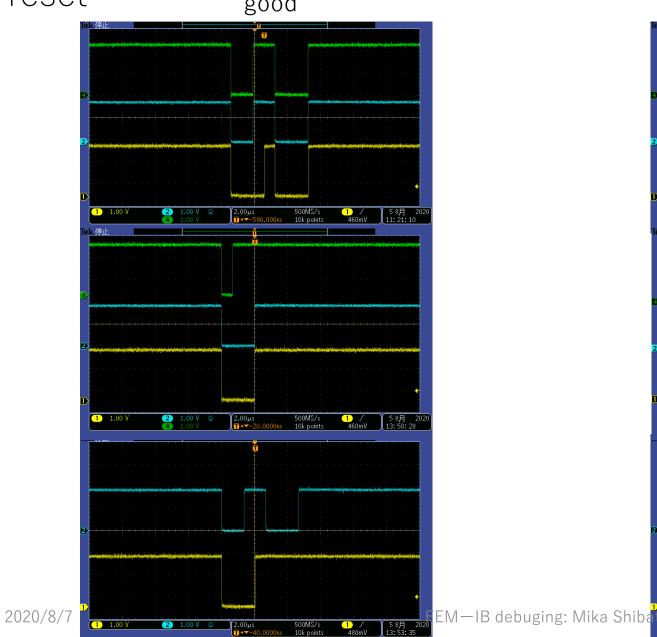

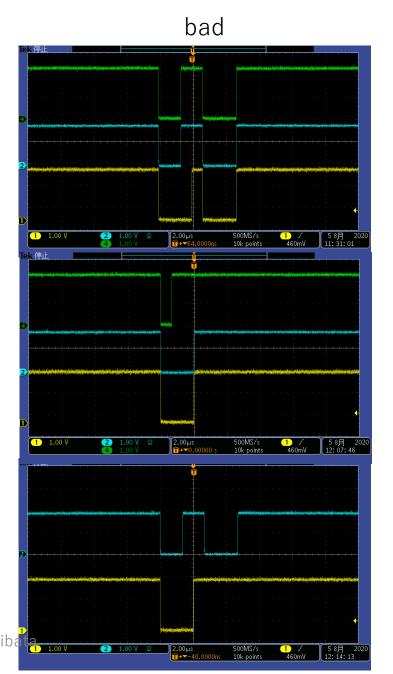

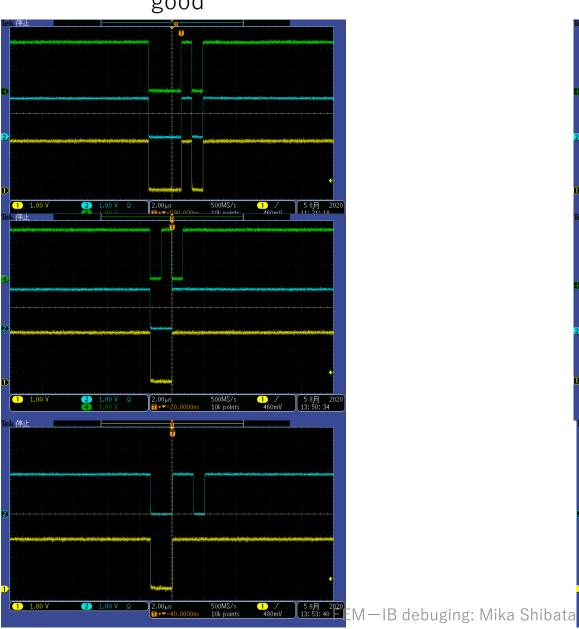

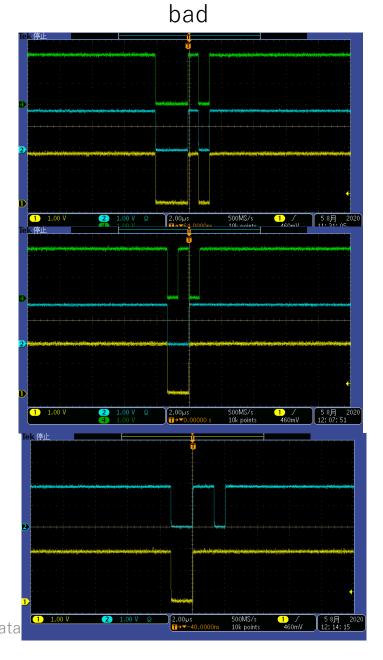

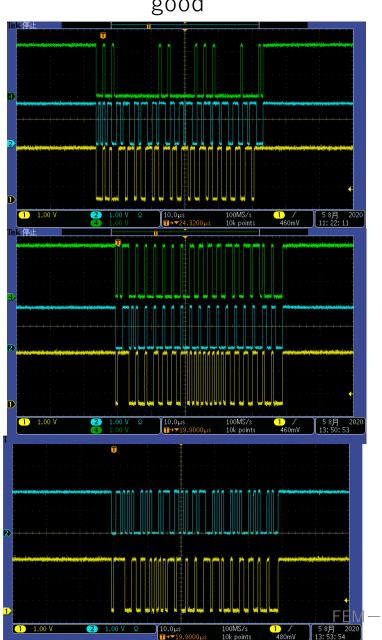

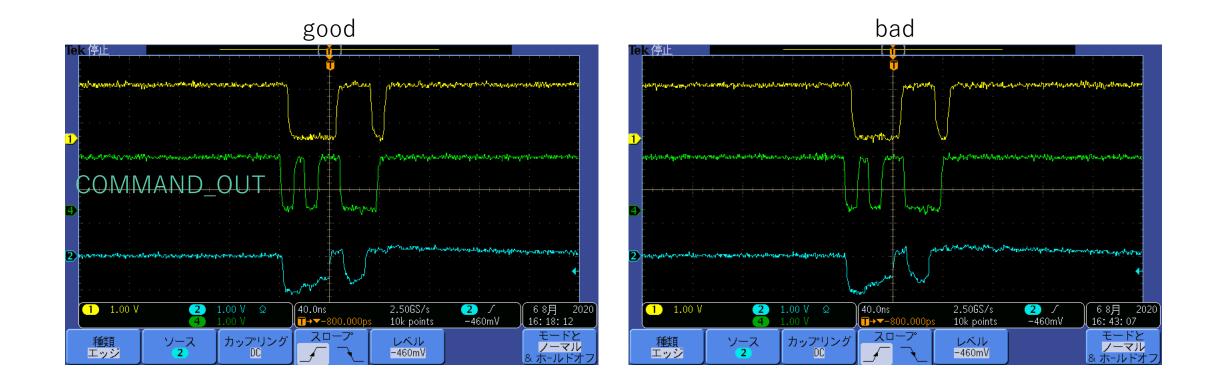

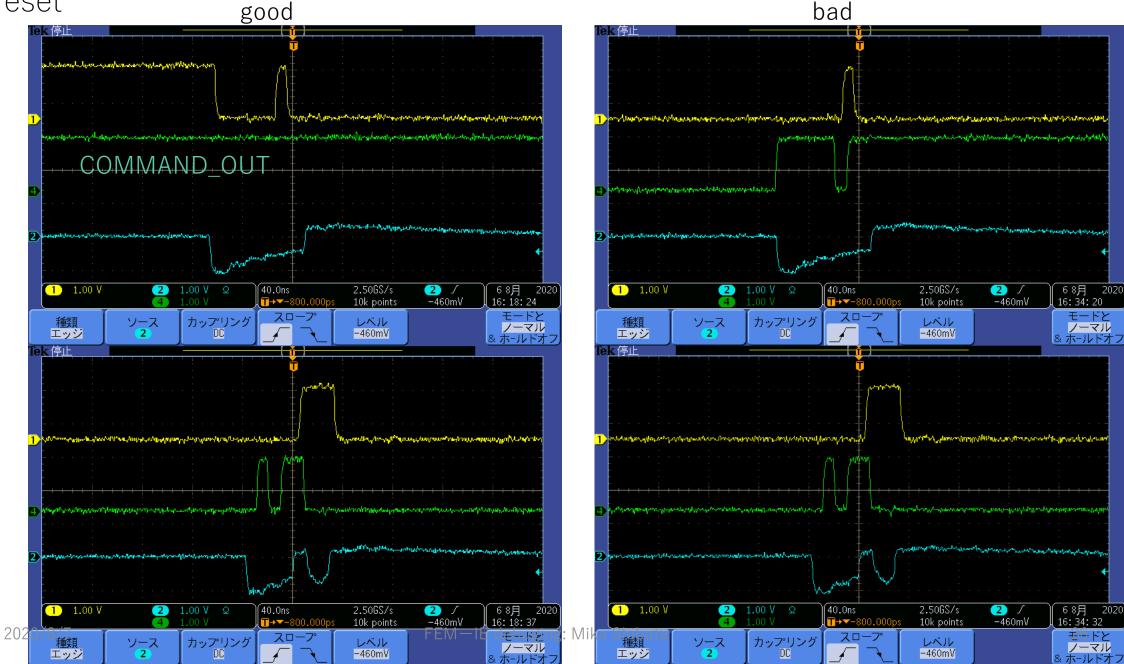

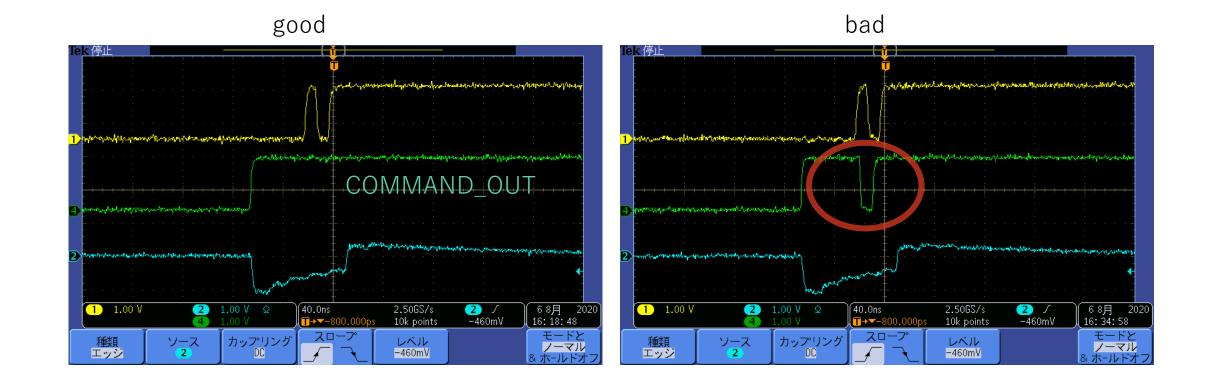

# Data from PC to ROC

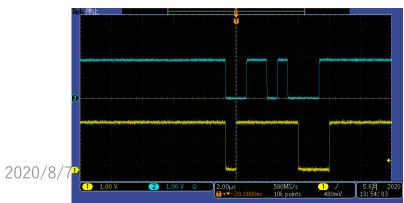

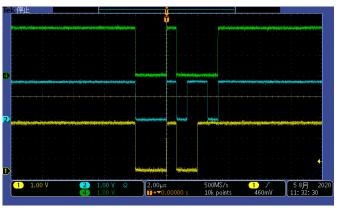

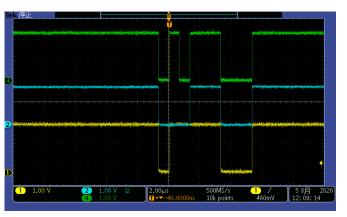

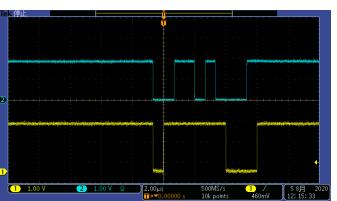

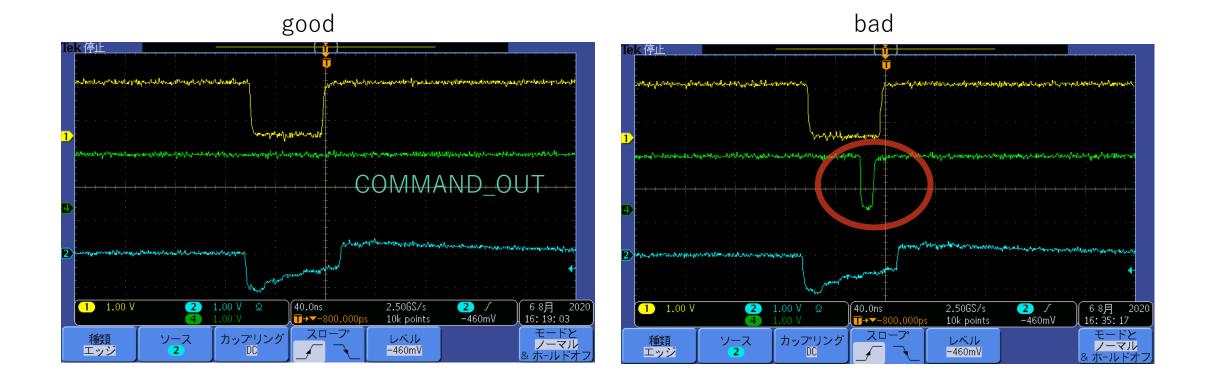

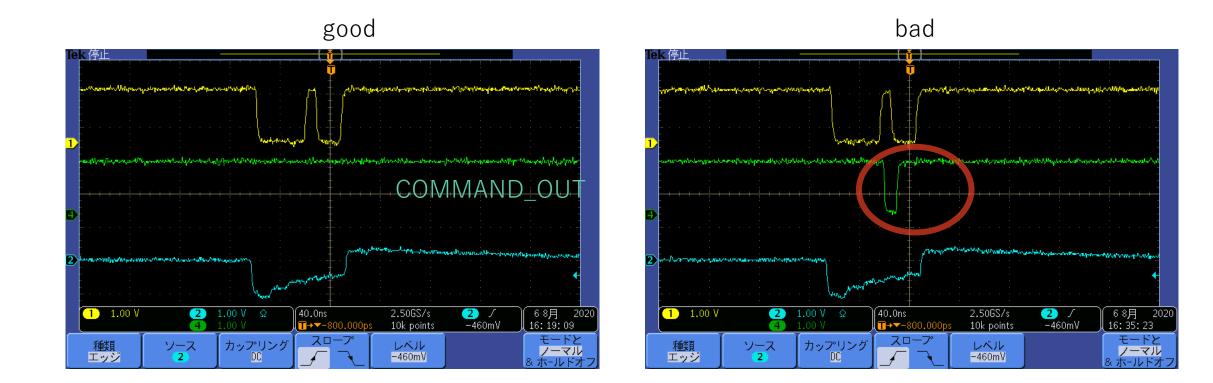

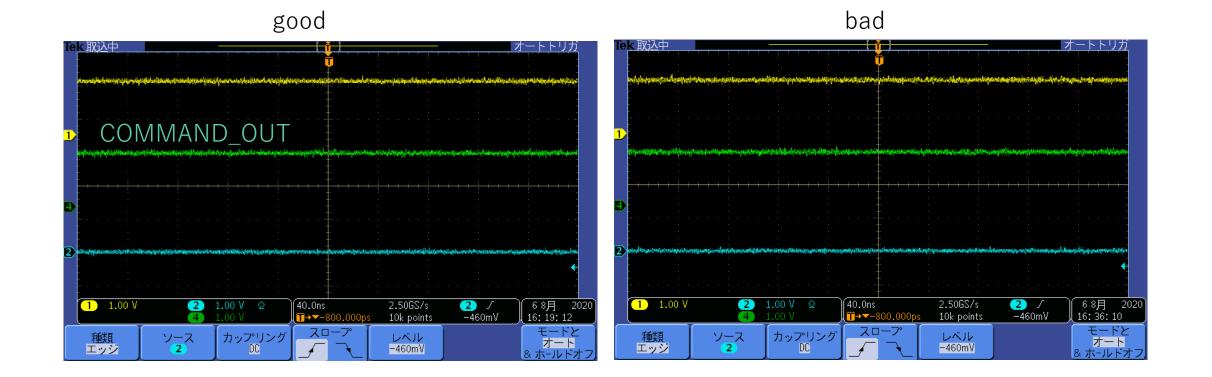

- We checked commands' signals from USB port on FEM-IB to SC port on FEM.

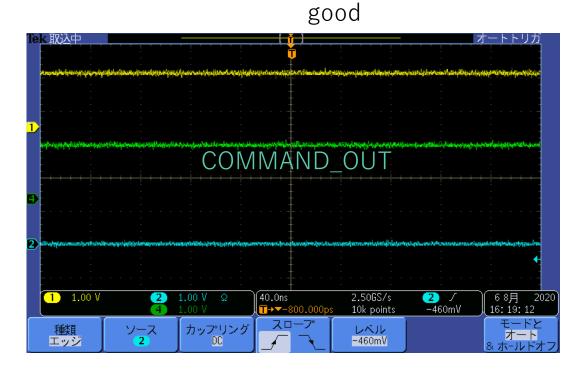

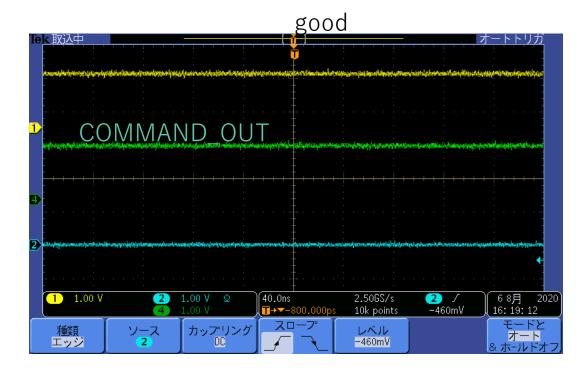

- 1. FEM-IB USB port can get data correctly.

- We compared **these signals** of good fem-ib and bad fem-ib.

- These signals are same.

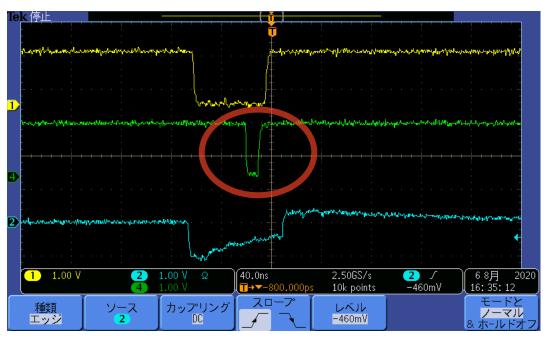

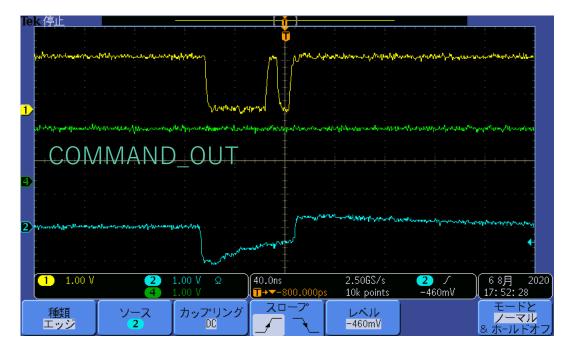

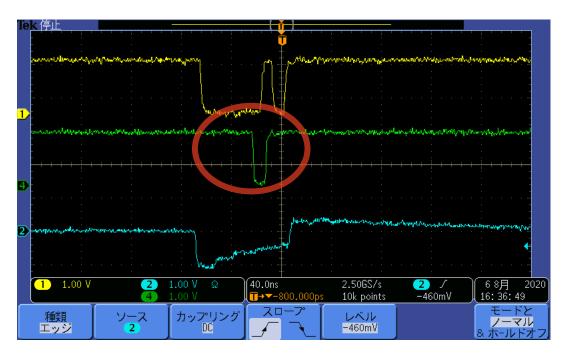

- 2. FEM SC port cannot get data correctly.

- We compared **these signals**.

- These signals are slightly different.

FEM board is same, so signals may break between FEM-IB and VME.

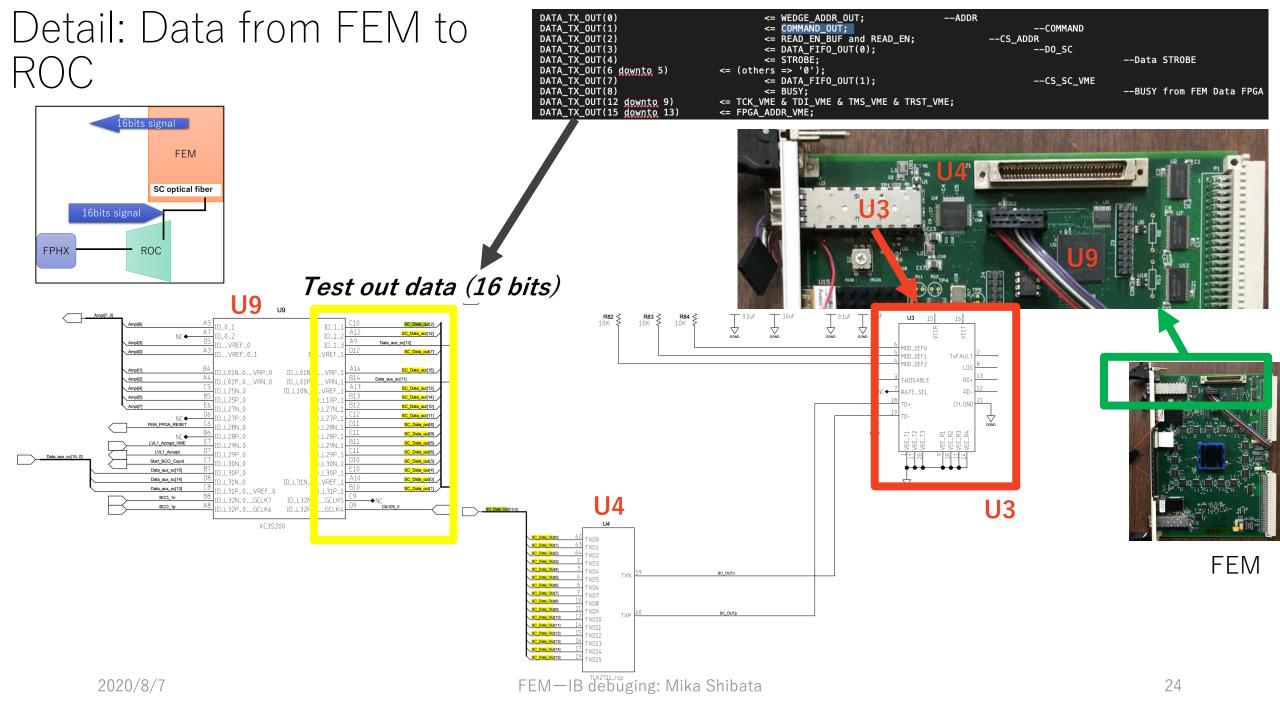

# Detail: Data from PC to ROC

## Detail: Data from PC to FEM-IB

## Detail: Data from PC to FEM-IB Fo sync good

2020/8/7

Detail: Data from PC to FEM-IB Fpga reset good

## Detail: Data from PC to FEM-IB ffr good

## Detail: Data from PC to FEM-IB init good

2020/8/7

## Detail: Data from PC to FEM-IB Enable ro good

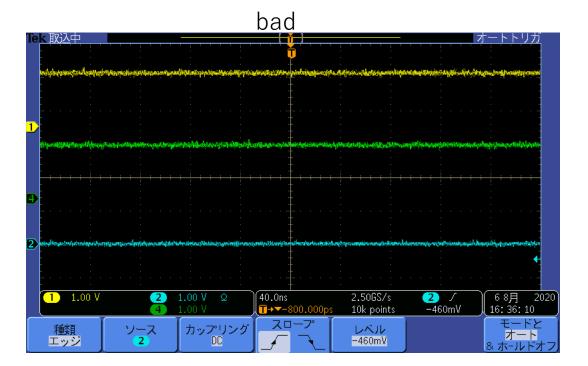

#### bad

FEM—IB debuging: Mika Shibata

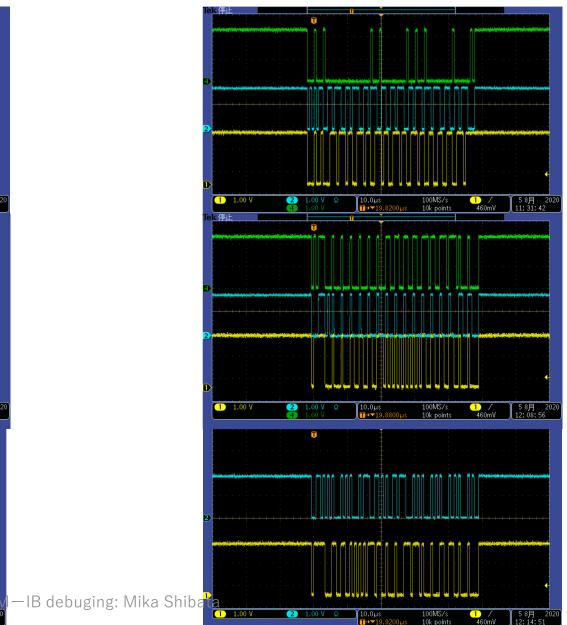

## Detail: Data from FEM to ROC FO SYNC

### Detail: Data from FEM to ROC Fpga reset

# Detail: Data from FEM to ROC ffr

# Detail: Data from FEM to ROC init

## Detail: Data from FEM to ROC Enable ro

## Detail: Data from FEM to ROC Latch fpga

## Detail: Data from FEM to ROC Set I1 delay

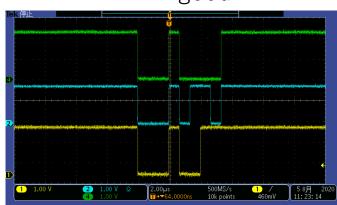

## Detail: Data from FEM to ROC Bco start

bad

| Te | <u>k 取込中</u>         |                                           |                                                                                                                 |                                            |                    |                    |                                         | _                         | オー                    | <u>トトリガ</u>                                     |

|----|----------------------|-------------------------------------------|-----------------------------------------------------------------------------------------------------------------|--------------------------------------------|--------------------|--------------------|-----------------------------------------|---------------------------|-----------------------|-------------------------------------------------|

|    |                      |                                           |                                                                                                                 |                                            |                    | Í Í                |                                         |                           |                       |                                                 |

|    | wisherproversite     | un anna anna anna anna anna anna anna a   | Nijepnovski ježelji i                                                                                           | Natiophysional National Market             | nannann            | Nakiminati         | nijani wakatanga ma                     |                           | and the second second | trout to const                                  |

|    | <br>                 |                                           |                                                                                                                 |                                            |                    |                    |                                         |                           |                       |                                                 |

|    | ·· · · ·             |                                           |                                                                                                                 |                                            |                    |                    |                                         |                           |                       |                                                 |

| 1  |                      |                                           |                                                                                                                 |                                            |                    |                    |                                         |                           |                       |                                                 |

| -  | Antonio Martinovilla | narie Piarted worklined in                | Heisseitheatheit                                                                                                | ushthabter and the latter                  | bhantlach astab    | Antonio Standia da | And and the state of the state          | an in the second second   | Witestie das Ambridas | novembelanes.                                   |

|    |                      |                                           |                                                                                                                 |                                            |                    |                    |                                         |                           | a floor a stiff of    |                                                 |

|    |                      |                                           |                                                                                                                 |                                            | <br>               |                    |                                         |                           |                       |                                                 |

| Ø  |                      |                                           |                                                                                                                 |                                            |                    |                    |                                         |                           |                       |                                                 |

|    |                      |                                           |                                                                                                                 |                                            |                    |                    |                                         |                           |                       |                                                 |

|    |                      |                                           |                                                                                                                 |                                            |                    |                    |                                         |                           |                       |                                                 |

| 2  |                      | et en | Programa de la composition de la compos | una di | escimitediarelfine | Anarana kanangkan  | (ing a sample of the same design of the | anidalamanaqiy napistisin | waadhaadhaa           | yaan yoo ka |

|    |                      |                                           |                                                                                                                 |                                            |                    |                    |                                         |                           |                       | •                                               |

|    |                      |                                           |                                                                                                                 |                                            |                    |                    |                                         |                           |                       |                                                 |

|    | 1 1.00               | ٧                                         | 2 1.                                                                                                            | .00 V Ω                                    | 40.0ns             |                    | 2.50GS/s                                |                           | 6                     | 8月 2020                                         |

| _  |                      |                                           | <u>(4) 1</u>                                                                                                    | .00 V                                      |                    | 300.000ps          | 10k point                               | s –460m                   |                       | : 36: 10                                        |

|    | 種類<br>エッジ            |                                           | -ス                                                                                                              | カップリング                                     | 끼 ~ ~              | <u>ープ</u>          | レベル                                     |                           |                       | モードと<br>オート                                     |

|    | エッジ                  |                                           | 2                                                                                                               | DC                                         |                    |                    | -460mV                                  |                           |                       | <u> </u>                                        |

## Detail: Data from FEM to ROC Calib

#### good

## Detail: Data from FEM to ROC Start DAQ

# Summary

- Commands' signals may break between FEM-IB and VME.

- Command signal is temporally drop off when we send command. (We expect that the signal must always be '1'. )