# INTT-SILICON LADDER PERFORMANCE

NARA WOMEN'S UNIVERSITY YUMIKA NAMIMOTO

1

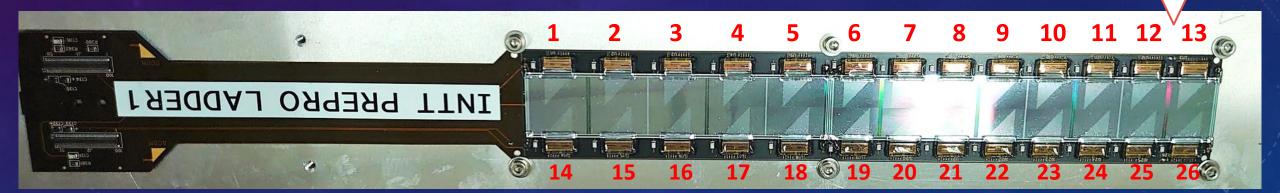

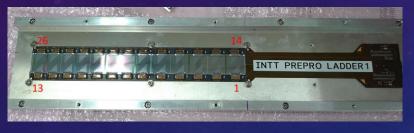

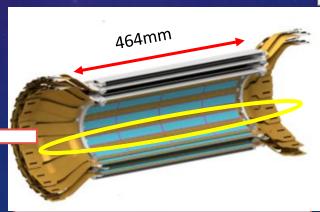

#### SILICON SENSOR

- INTT-silicon ladder is consisted of silicon semiconductor, readout chip (namely FPHX) and HDI. If charged particles pass through, it takes data.

- In half ladder, 26 FPHX chips are exist and it reads signals come from silicon ladder

- Full ladder consisted of 2 half ladder, so it has 52 FPHX chips.

#### Half ladder

#### CHIP NUMBER, CHANNEL NOMENCLATURE

- We divide silicon ladder for 26 area.

- 1 area correspond 1 FPHX chip.

- 1 chip divide 128 channels. Channel size is  $78\mu m \times 16(or20)mm$ .

- In silicon sensor, outside is channel 0 and inside is channel127.

127 127

...

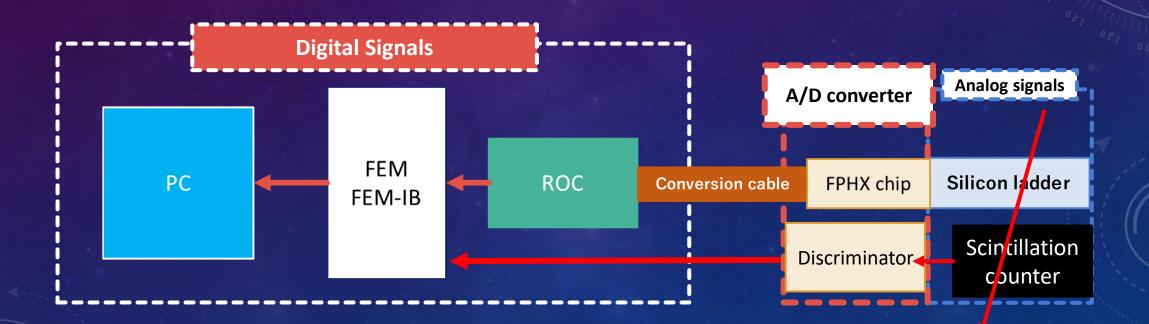

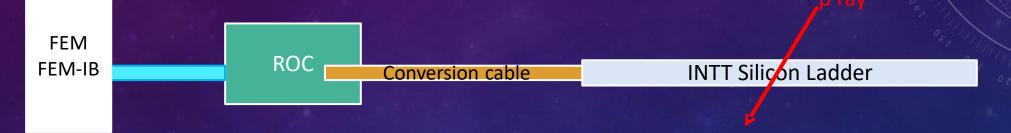

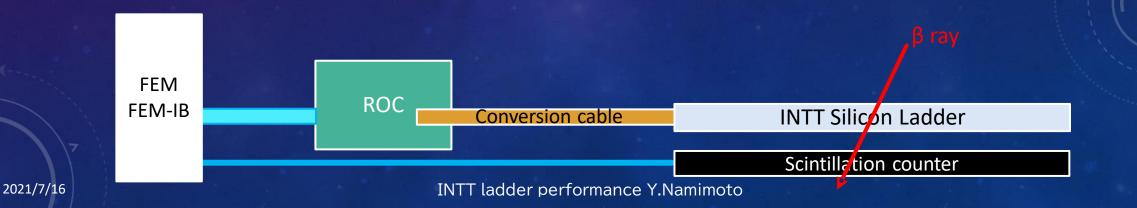

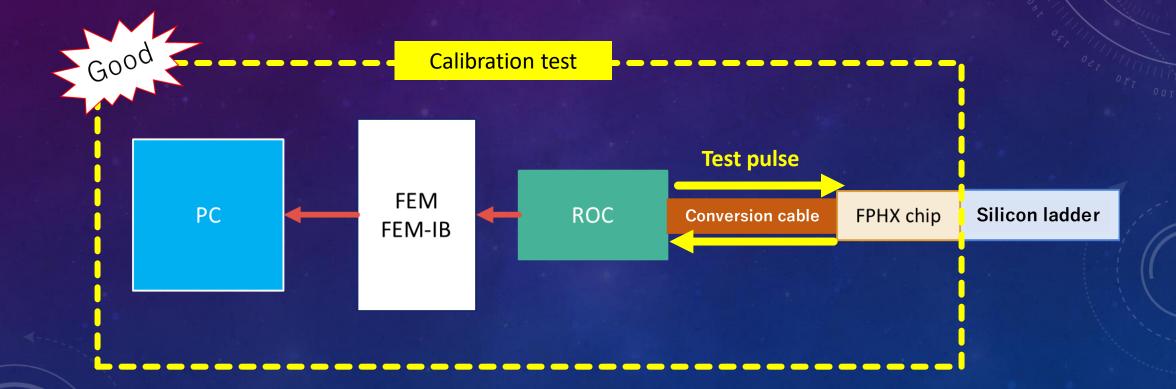

#### DATA READOUT CIRCUIT

- If silicon ladder detects charged particle, analog signals send to FPHX chips.

- FPHX chips convert analog signals to digitals, and the signals are sent to ROC(Read Out Card) through the conversion cable.

- Digital signals are processed at ROC and later FEM and recorded by PC.

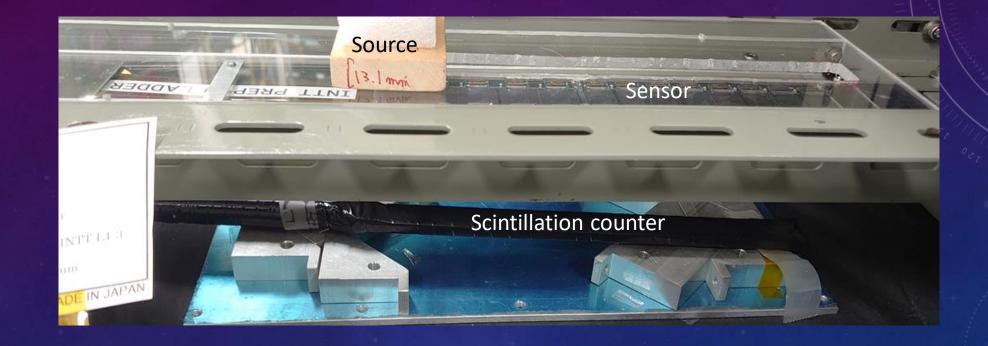

#### TEST BENCH IN NWU

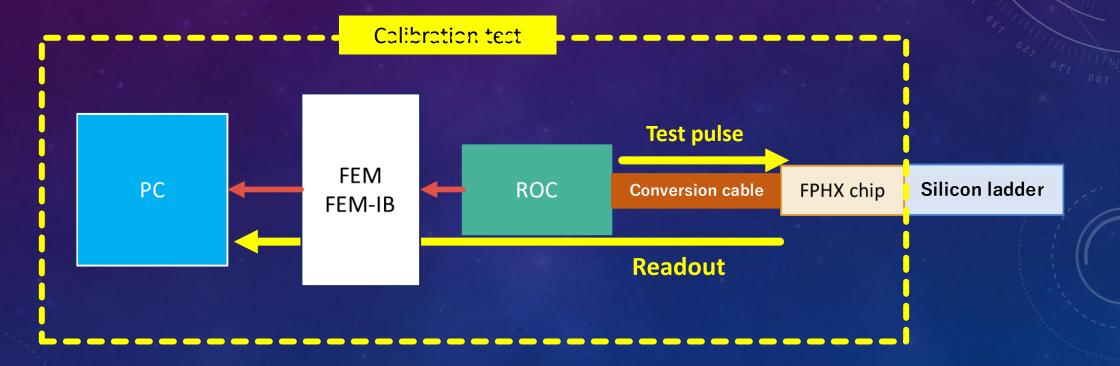

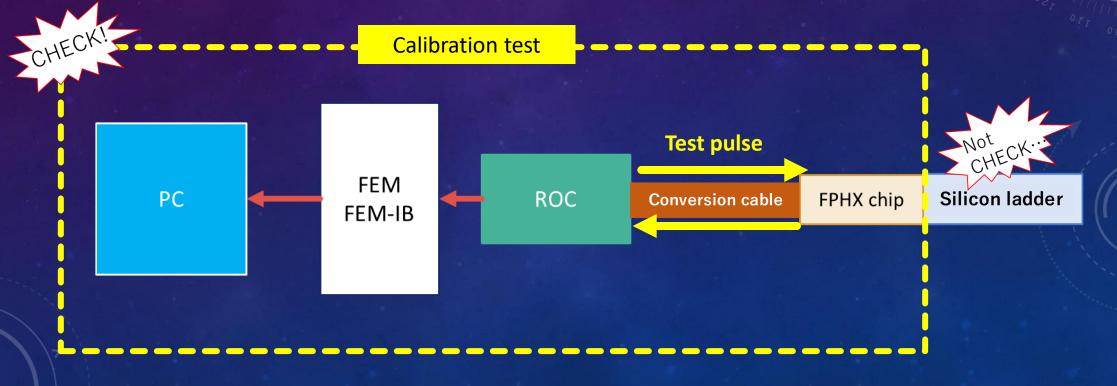

### CALIBRATION TEST

- <u>Calibration test</u>: We send test pulse to FPHX chips from ROC and compare the received data with input pulses.

- 10 test pulses are send to 1 channel.

- We can check the operation about PC, FEM, FEM-IB, ROC and FPHX chips, without silicon ladder.

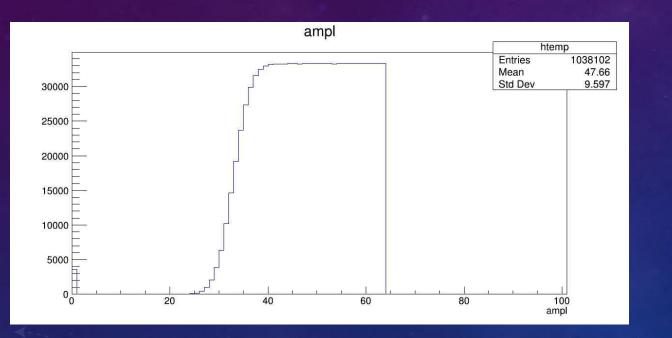

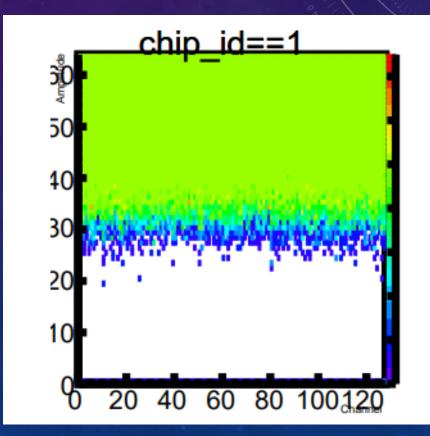

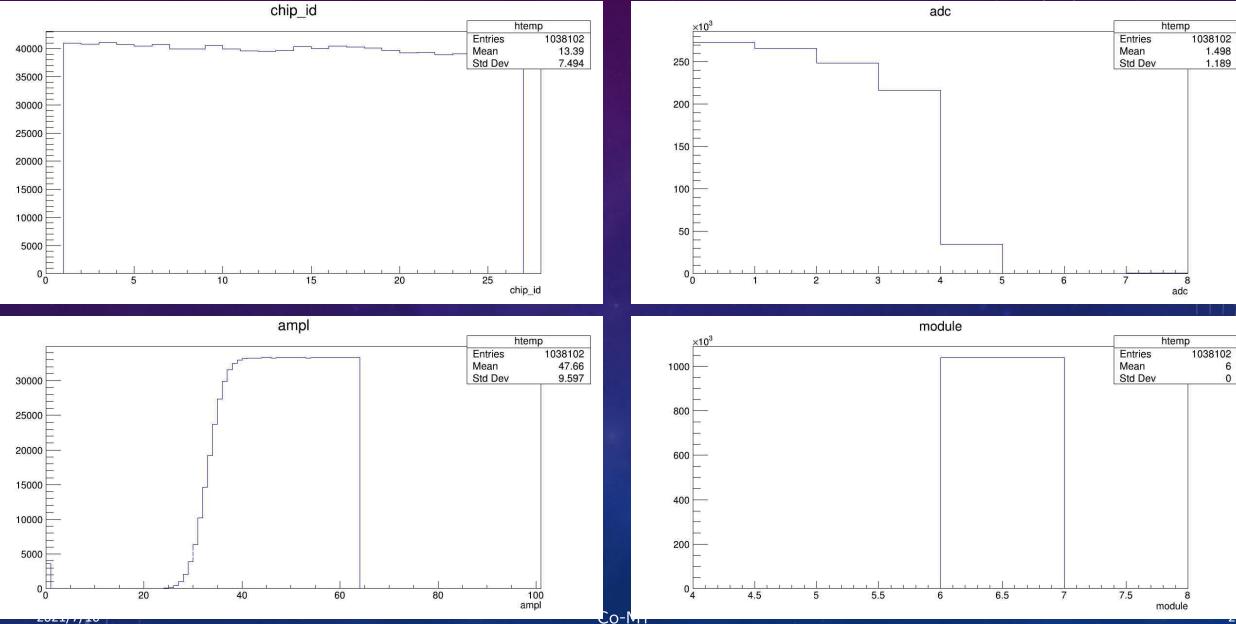

- <u>Amplitude vs channel</u>

- Test pulses are sent to all channels, all chips.

- We confirm from this plot that each channels received test pluses and how the threshold is scattering.

7

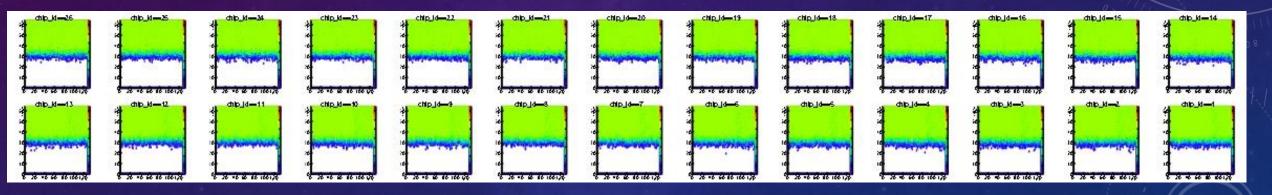

• This picture shows the result of all chips in half ladder .

- Chips line up like black picture.

- All channels in 26 chips operate.

- Thresholds are not scattering.

| 0                      |    |    |    |    |    |    |    |    |    |    |    |    |    | 0                      |

|------------------------|----|----|----|----|----|----|----|----|----|----|----|----|----|------------------------|

| 1<br>2<br><br>127      | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 1<br>2<br><br>127      |

| 127<br><br>2<br>1<br>0 | 13 | 12 | 11 | 10 | 9  | 8  | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 127<br><br>2<br>1<br>0 |

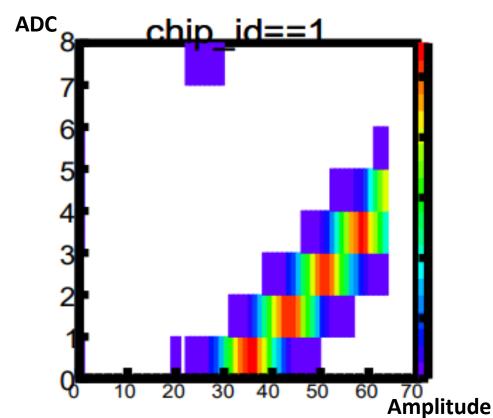

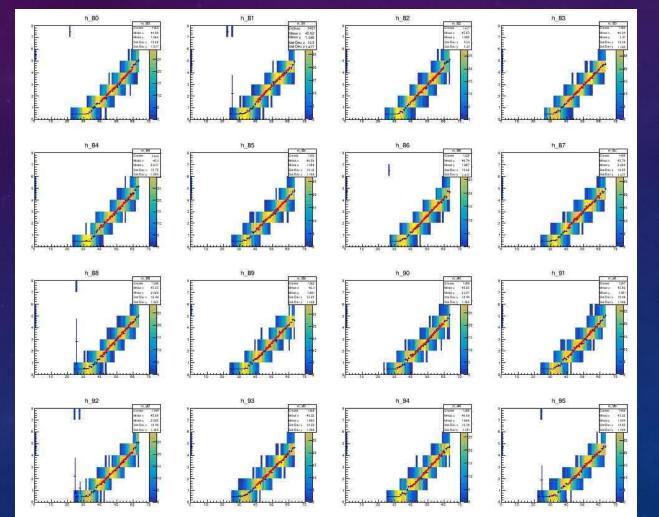

- <u>ADC vs amplitude</u>

- This plot shows the correlation between the amplitude and output.

- Amplitude is input pulse height of the test pulse and ADC is output data.

- In this plot, output ADC is proportional to the input amplitude.

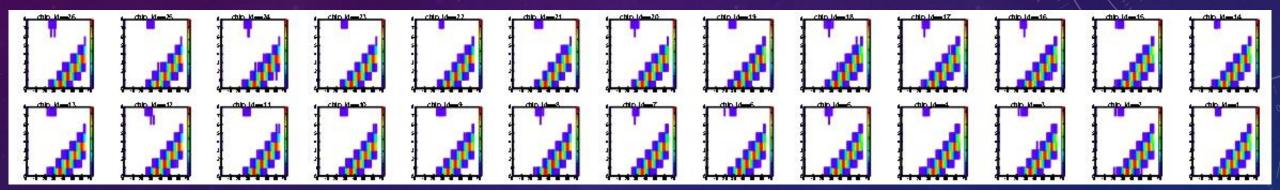

• This picture shows the plots of all chips in half ladder.

Linearity of ADC is confirmed in all chips.

#### SOURCE TEST

- <u>Source test</u>: Silicon sensor detects  $\beta$  particles,  $e^-$  from  $\beta$  source  ${}^{90}$ Sr.

- $e^-$  from the source: It has many entries and low energies, and we can control hit spot.

- Cosmic rays: It has less entries and high energies, and we cannot control hit spot.

## 2 WAYS FOR SOURCE TEST

#### Self trigger test

- We use only silicon ladder.

- If silicon ladder detects charged particle, we get data.

#### External trigger test

- We use silicon ladder and something for external trigger module, like scintillation counter.

- If both silicon ladder and external trigger module detect charged particle, we get data.

### SOURCE TEST: SELF TRIGGER RESULT

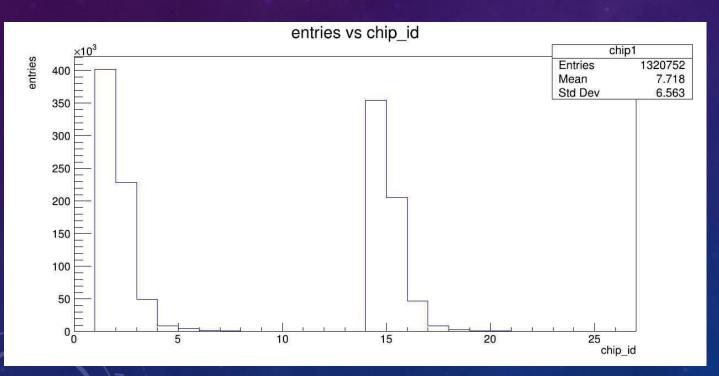

• We set <sup>90</sup>Sr on chip 1 and did self trigger test.

| 0                              |      |    |    |    |    |    |    |    |    |    |    |    |    |                        |

|--------------------------------|------|----|----|----|----|----|----|----|----|----|----|----|----|------------------------|

| <sup>2</sup> / <sub>2</sub> 90 | Sr   | 2  | 3  | 4  | 5  | 6  | 7  | 8  | 9  | 10 | 11 | 12 | 13 | 2<br><br>127           |

| 127<br><br>2<br>1<br>0         | L4 1 | 15 | 16 | 17 | 18 | 19 | 20 | 21 | 22 | 23 | 24 | 25 | 26 | 127<br><br>2<br>1<br>0 |

- Chip1, the chip closest to the source has largest entries.

- Around chip1 chips, chip2,3,14,15 has many entries.

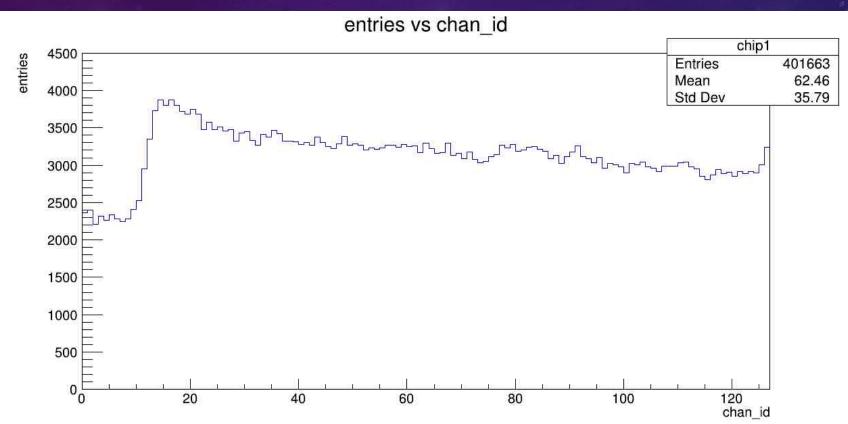

### SOURCE TEST: SELF TRIGGER RESULT

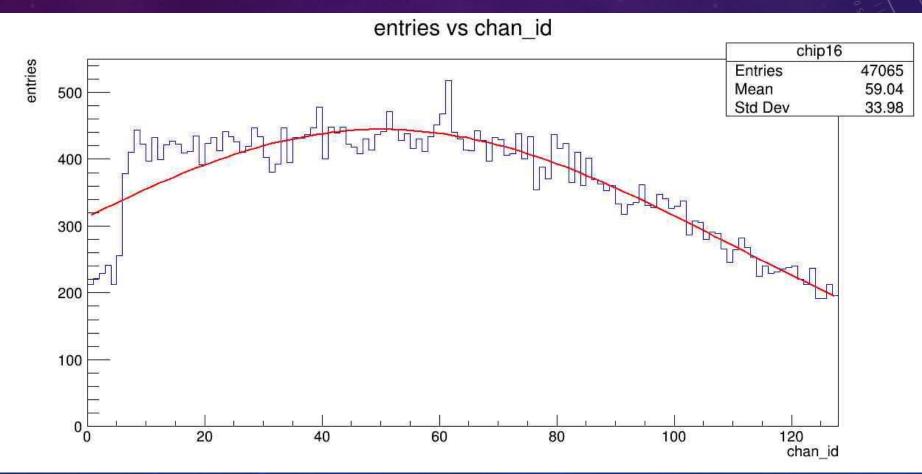

- This picture shows chip1-channel distribution.

- Channel 0-10 have less entries than it expected. This phenomena occur in all chips.

- $\rightarrow$ Is  $\beta$  ray cannot entry to channel 0-10? Or another reasons exists?

- $\rightarrow$ We try to external trigger test.

• We use scintillation counter for external trigger.

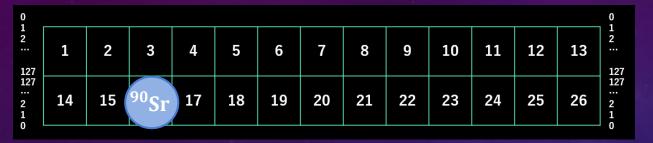

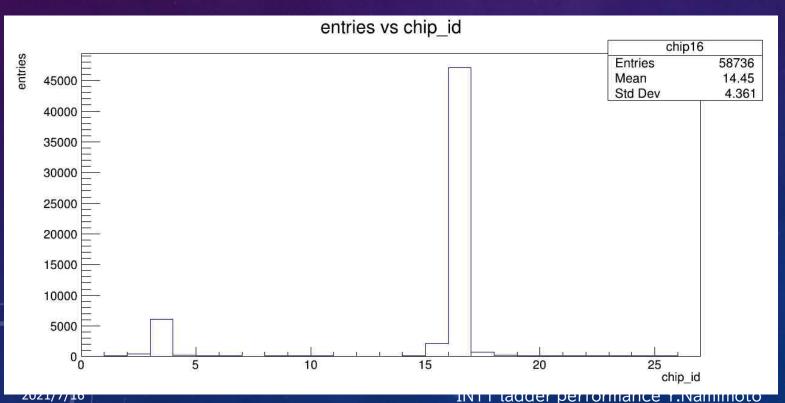

- We set β source on chip16 and did external trigger test.

- Channel 0-10 should have hits by  $\beta$  ray.

Chip16 has the largest entries, and chip3, close to source chip has the 2nd largest entries.

16

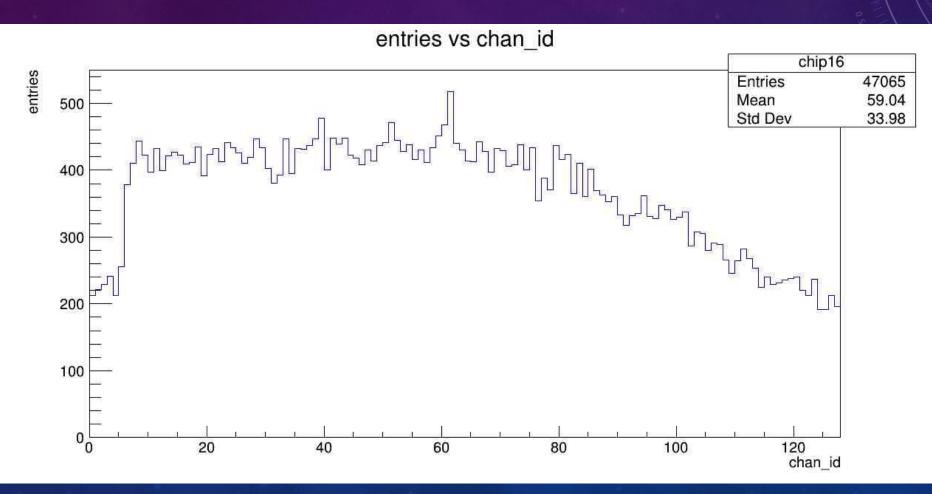

- This picture shows chip16-channel distribution.

- Channel 0-10 have low entries.

- I try to fit the hit channel distribution with Gaussian.

- Fit range is channel 70-127 to evaluate the hit shape.

- It shows that channel 0 is expected about 320 entries, but it has only 220 entries.

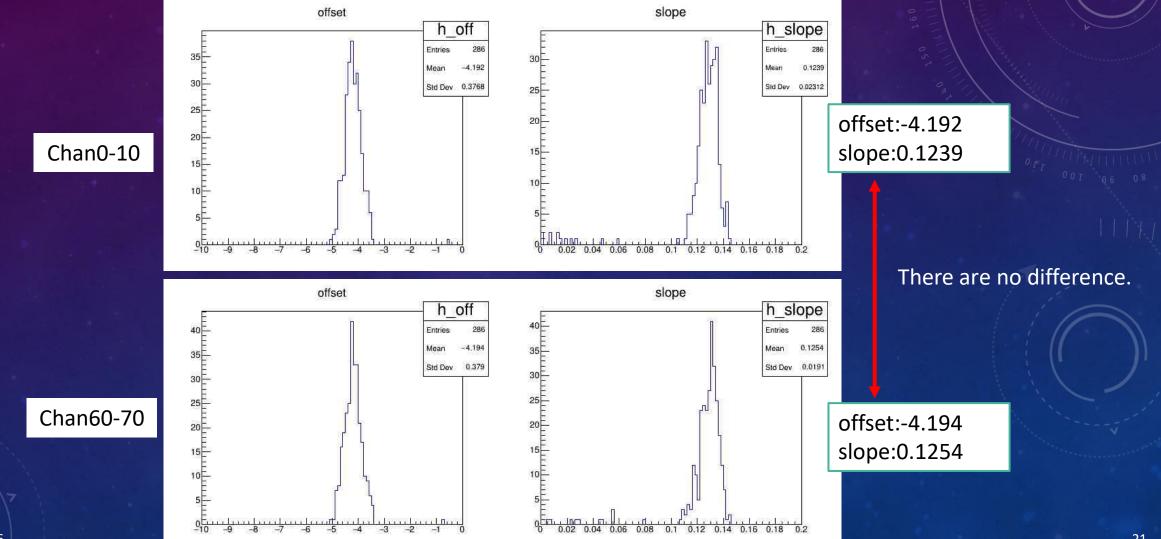

- I try to search which module cause this phenomena.

- <u>Calibration test</u> uses FPHX chips, ROC, FEM, FEM-IB and PC, without silicon ladder. If the result shows something strange, it is expected that these modules cause this phenomena. If it does not, silicon ladder causes this phenomena.

- I compare calibration test result of slope and offset at ADC vs amplitude.

- This program made by Dr. Hachiya.

- Left pictures show offset and right pictures show slope of ADC vs amplitude.

- Upper picture is about channel 0-10, and bottom is channel 60-70.

- Calibration test does not show strange result.

- $\rightarrow$ The phenomena are caused by between FPHX chip and silicon ladder, or only silicon ladder.

#### SOURCE TEST SUMMARY

- We find low efficiency issue at channel 0-10.

- No suspicious behavior was observed in the calibration results for the ladder. So the issue can be caused by between FPHX chips and silicon ladder, or only silicon ladder.

- We can check silicon ladder's operation easily and rapidly by using radiation source.

- The next step is to investigate silicon ladders response using a radiation source test fixture.

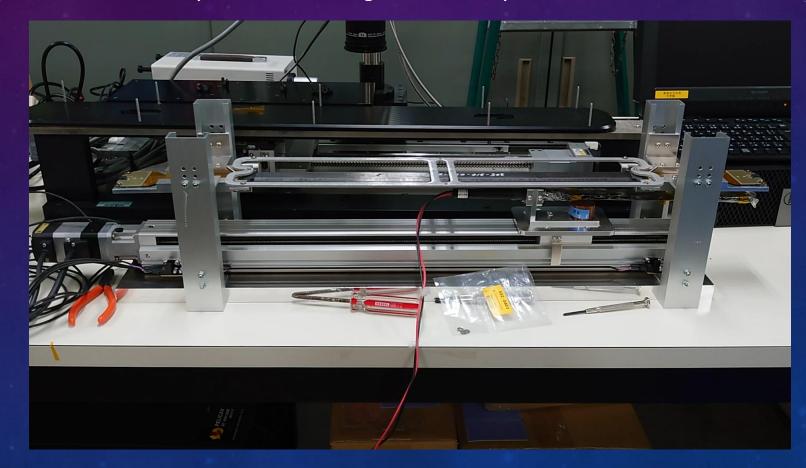

#### SOURCE TEST FIXTURE

- Now, we get source test fixture. Toward sPHENIX experiment start in 2023, now we mass product silicon ladders, so we should check all ladders rapidly.

- Using this fixture, Radiation source move automatically. We can expose all 26 chips to β ray in one time, automatically. It is useful to many sensors checking automatically.

#### SUMMARY

- We can see the signals from  $\beta$  source by using silicon ladder.

- We developed 2 methods to test the INTT ladder.

- Calibration test is useful to check if the readout system including channel-by-channel response works or not.

- Source test is useful to see the response of the radiation.

- Now we check source test fixture operation. Sometimes it takes noises, so we try to search noise source and remove the signals.

• After we understand the fixture operation, we will be able to check many ladders easily and rapidly.

# BACK UP

#### CALIBRATION TEST

2021/7/10

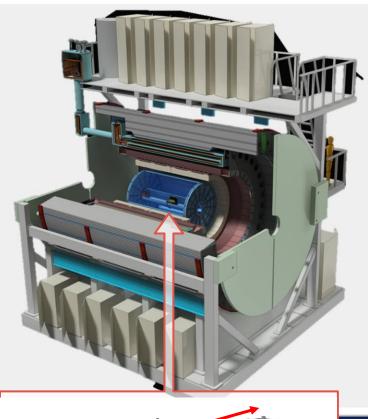

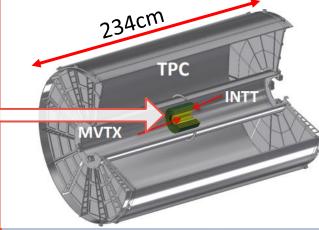

### ABOUT INTT

- INTT(INTermadiate Tracker) is a detector of SPHENIX experiment.

- One of three track detectors where is close to collision point.

- It is consisted by silicon semiconductor, if charged particle comes through, it takes data.

#### Half ladder

#### Full ladder

#### ABOUT ADC

- We can set thresholds of silicon sensor from PC.

- ADC value can change to mV value by bottom equation.

|      | Default |      |  |  |  |  |  |  |  |  |

|------|---------|------|--|--|--|--|--|--|--|--|

|      | ADC     | mV   |  |  |  |  |  |  |  |  |

| DAC0 | 10      | 250  |  |  |  |  |  |  |  |  |

| DAC1 | 23      | 302  |  |  |  |  |  |  |  |  |

| DAC2 | 48      | 402  |  |  |  |  |  |  |  |  |

| DAC3 | 98      | 602  |  |  |  |  |  |  |  |  |

| DAC4 | 148     | 802  |  |  |  |  |  |  |  |  |

| DAC5 | 172     | 898  |  |  |  |  |  |  |  |  |

| DAC6 | 223     | 1102 |  |  |  |  |  |  |  |  |

| DAC7 | 248     | 1202 |  |  |  |  |  |  |  |  |

### Threshold(mV)=ADC $\times$ 4 + 210(mV)