# ALPIDE for MVTX and the next steps

Y. Kwon (Yonsei Univ.)

# ALPIDE(ALice Plxel DEtector)

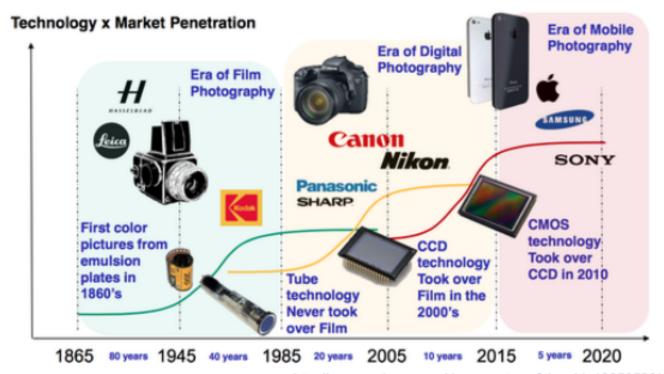

#### MAPS Evolution

L. Musa, 30 years HI Forum November 2016

Owing to the industrial development of CMOS imaging sensors and the intensive R&D work (IPHC, RAL, CERN)

... several HI experiments have selected CMOS pixel sensors for their inner trackers

STAR HFT 0.16 m<sup>2</sup> – 356 M pixels

**CBM MVD** 0.08 m<sup>2</sup> – 146 M pixel

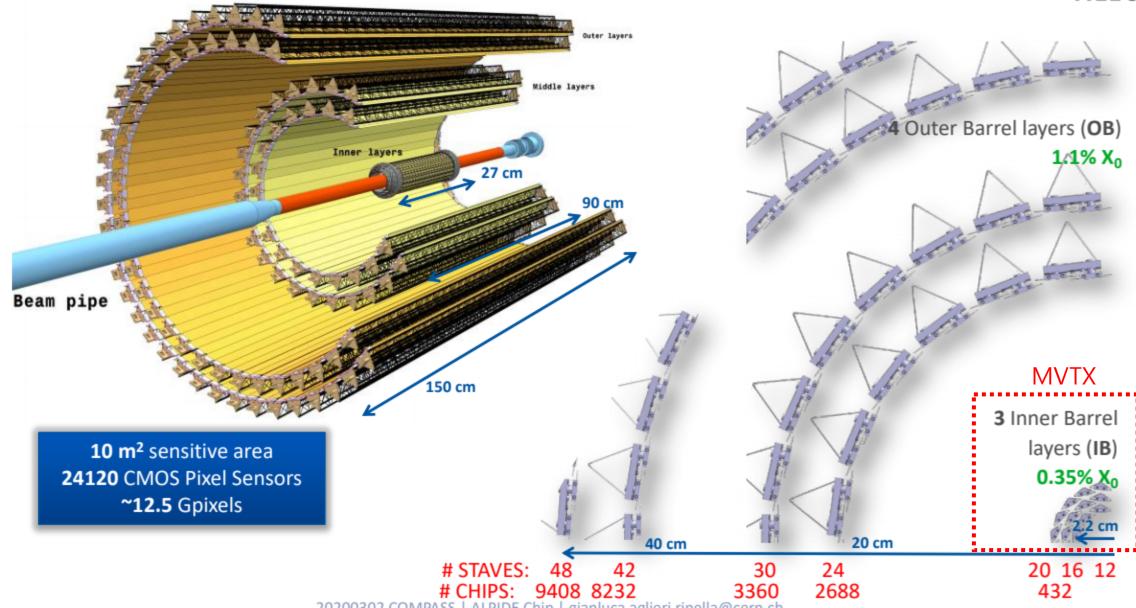

ALICE ITS Upgrade (and MFT) 10 m<sup>2</sup> – 12 G pixel

0.2 m<sup>2</sup> - 251 M pixel

20

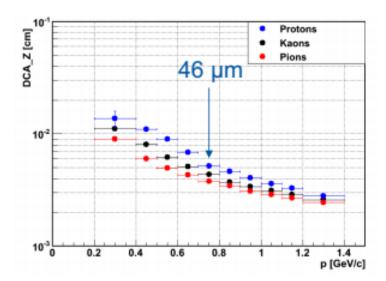

#### STAR HFT

- DCA pointing resolution

- Design requirement exceeded: 46 µm for 750 MeV/c Kaons for the 2 sectors equipped with aluminum cables on inner layer

- > ~ 30 μm for p > 1 GeV/c

- From 2015: all sectors equipped with aluminum cables on the inner layer

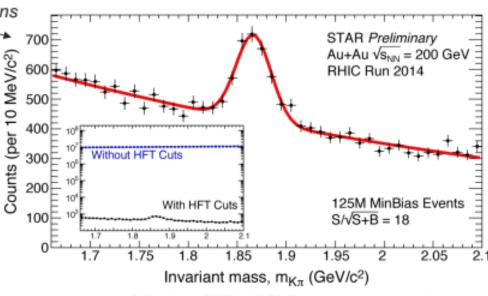

$D^0$  → K  $\pi$  production in  $\sqrt{s_{NN}}$  = 200GeV Au+Au collisions (partial event sample)

- High significance signal

- Nuclear modification factor R<sub>AA</sub>

- Collective flow v<sub>2</sub>

- First Λ<sub>c</sub><sup>+</sup> signal observed in HI collisions (QM 2017)!

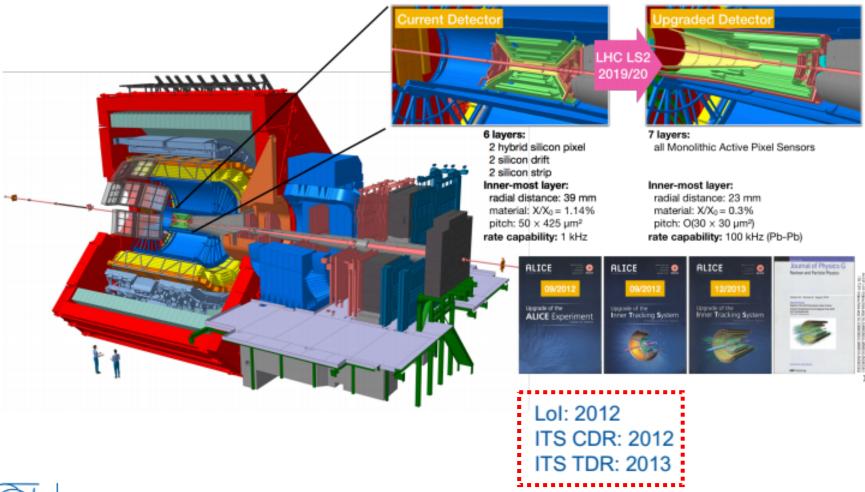

## ALICE Upgrade

#### Motivation: QGP precision study

High precision measurement of heavy flavour hadrons over a large range in p<sub>T</sub> and rapidity and multi-differentially in centrality and reaction plane.

#### Requirements:

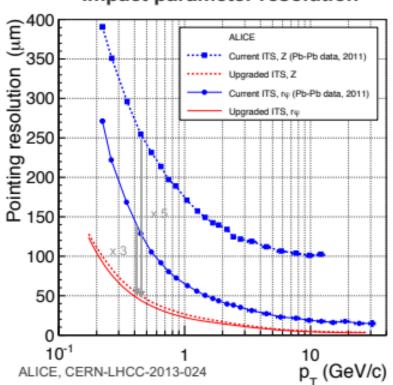

- Excellent tracking efficiency and resolution at low p<sub>T</sub>

- Large statistics with minimum bias trigger to gain a factor 100 over present program

- Pb-Pb recorded luminosity ≥10 nb<sup>-1</sup> plus p-p and p-A data

- Preserve PID capability at high rate

#### Strategy:

- Readout all Pb-Pb interactions at max. rate (50 kHz) with minimum bias trigger

- Upgrade of the detector readout and online and offline systems

- Large improvement of vertexing and tracking capability

- New Inner Tracking System (ITS) and Muon Forward Tracker (MFT)

## ITS Chip General Requirements

| Parameter                                                              | Inner Barrel                                                                           | Outer Barrel           |

|------------------------------------------------------------------------|----------------------------------------------------------------------------------------|------------------------|

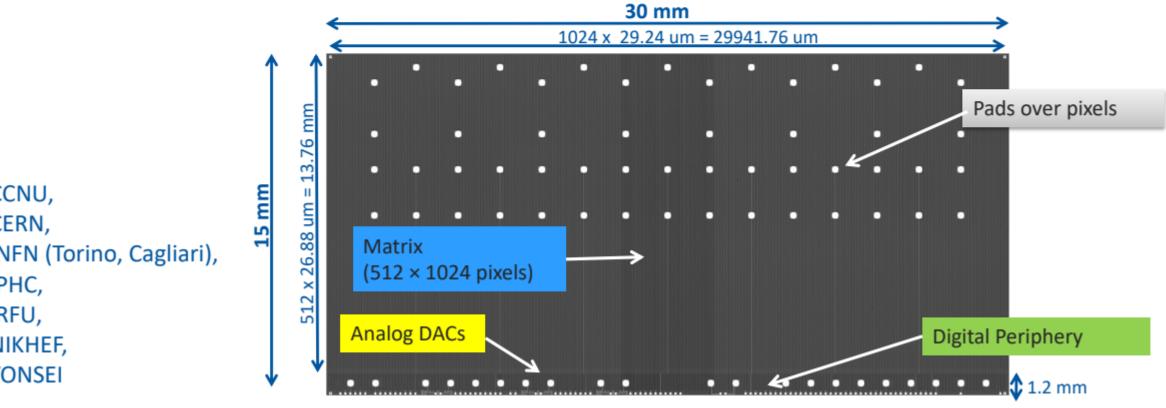

| Chip size (mm x mm)                                                    | 15 x 30                                                                                |                        |

| Chip thickness (µm)                                                    | 50                                                                                     | 100                    |

| Spatial resolution (μm)                                                | 5                                                                                      | 10 (5)                 |

| Detection efficiency                                                   | > 99%                                                                                  |                        |

| Fake hit rate                                                          | < 10 <sup>-5</sup> evt <sup>-1</sup> pixel <sup>-1</sup> (ALPIDE << 10 <sup>-5</sup> ) |                        |

| Integration time (µs)                                                  | < 30 (< 10)                                                                            |                        |

| Power density (mW/cm²)                                                 | < 300 (~35)                                                                            | < 100 (~20)            |

| TID radiation hardness (krad) (**)                                     | 2700                                                                                   | 100                    |

| NIEL radiation hardness (1 MeV n <sub>eq</sub> /cm <sup>2</sup> ) (**) | 1.7 x 10 <sup>13</sup>                                                                 | 1.7 x 10 <sup>12</sup> |

| Readout rate, Pb-Pb interactions (kHz)                                 | 100                                                                                    |                        |

| Hit Density, Pb-Pb interactions (cm <sup>-2</sup> )                    | 18.6                                                                                   | 2.8                    |

<sup>(\*)</sup> In color: ALPIDE performance figure where above requirements

<sup>(\*\*) 10</sup>x radiation load integrated over approved program (~ 6 years of operation)

## **ALICE ITS Upgrade Layout**

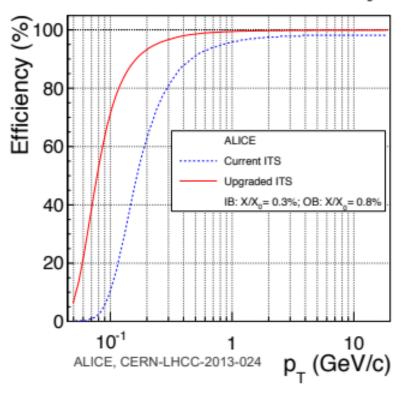

#### ALICE ITS Upgrade Performance Studies

#### Impact parameter resolution

Improved impact parameter resolution

February 22, 2018

#### Track reconstruction efficiency

High standalone tracking efficiency

# ALPIDE, Technology

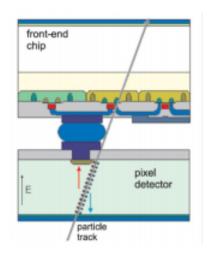

## Hybrid and Monolithic Pixels

- Separately optimize sensor and FE-chip

- Fine pitch bump bonding to connect sensor and readout chip

- Charge generation volume integrated into the ASIC, but many different variants!

- Thin monolithic CMOS sensor, on-chip digital readout architecture

## **CMOS Image Pixel Sensors**

- While 1980s were dominated by CCDs (camcorder market)

- The 1990s/2000s have shown an increasing demand for CMOS imaging sensors due to the camera phone market

http://www.eetimes.com/document.asp?doc\_id=1325655&image\_number=1

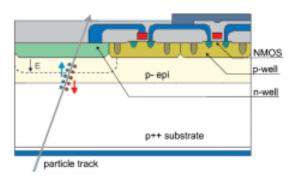

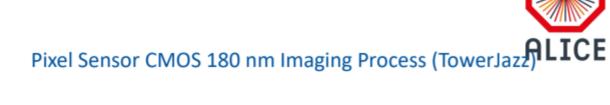

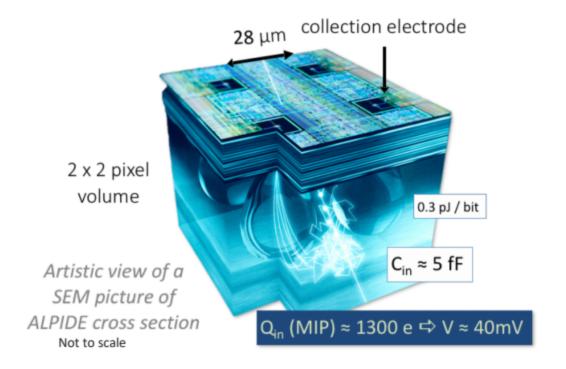

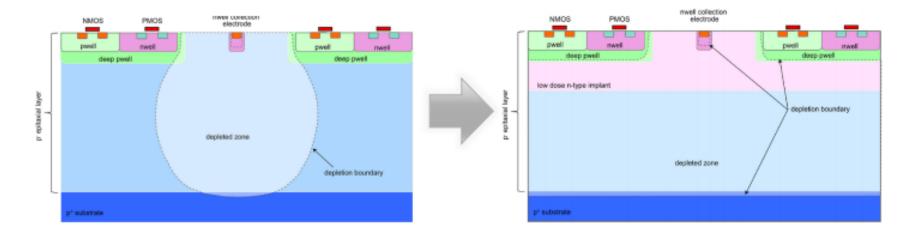

#### **ALPIDE Technology**

High-resistivity (>  $1k\Omega$  cm) p-type epitaxial layer (~25  $\mu$ m) on p-type substrate

Deep PWELL shielding NWELL allowing PMOS transistors (full CMOS within active area)

Small n-well diode (2 μm diameter), ~100 times smaller than pixel => low capacitance => large S/N

Reverse bias can be applied to the substrate to increase the depletion volume around the NWELL collection diode

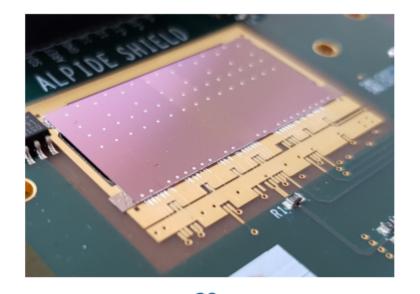

## **ALPIDE Chip**

PHC, RFU, IIKHEF, ONSEI

CNU,

ERN,

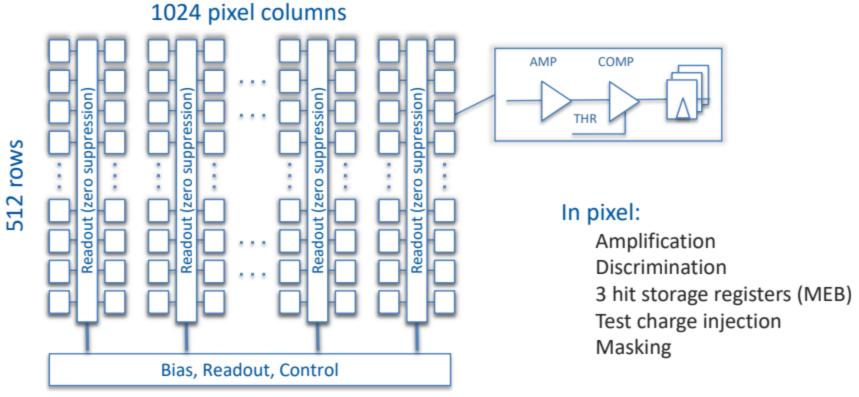

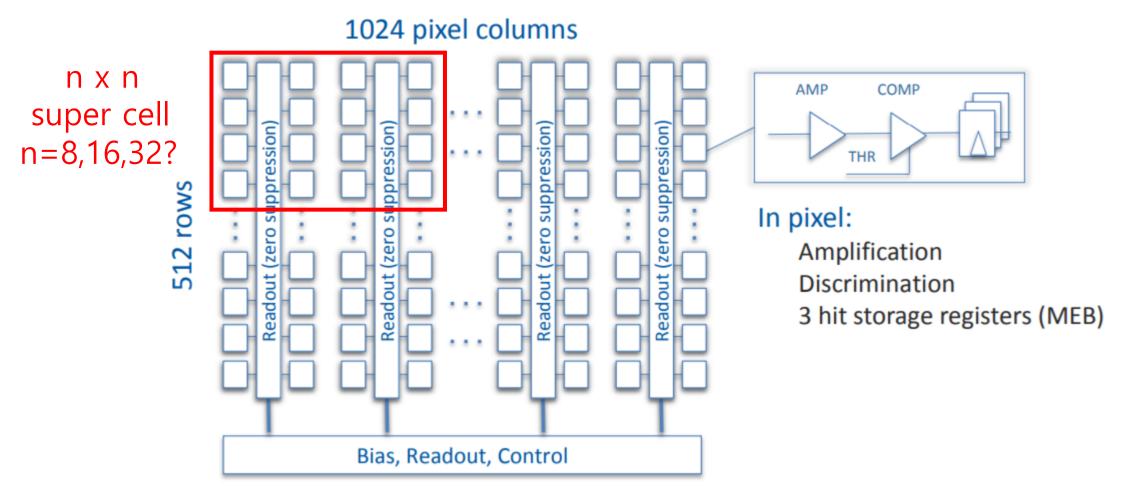

#### **Pixel**

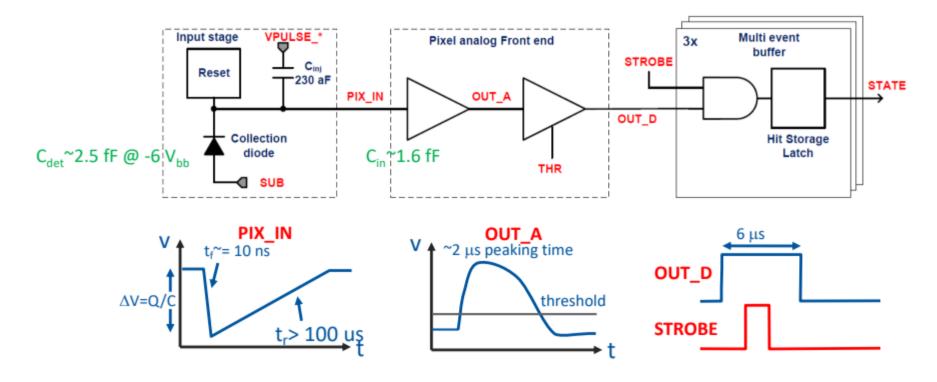

#### Analog front-end and discriminator continuously active

Non-linear and operating in weak inversion. Ultra-low power: 40 nW/pixel

The front-end acts as analogue delay line

Test pulse charge injection circuitry

Global threshold for discrimination -> binary pulse OUT\_D

#### Digital pixel circuitry with three hit storage registers (multi event buffer)

Global shutter (STROBE) latches the discriminated hits in next available register In-Pixel masking logic

| Front End Characteristics (simulated) |        |  |

|---------------------------------------|--------|--|

| Gain (small signal) [mV/e]            | 4      |  |

| ENC [e]                               | 3.9    |  |

| Threshold [e]                         | 92 ± 2 |  |

#### **ALPIDE Architecture**

$29 \mu m \times 27 \mu m$  pixel pitch

Continuously active front-end

Global shutter (STROBE signal)

Zero-suppressed matrix readout

Triggered or continuous readout modes

# ALPIDE, Performance

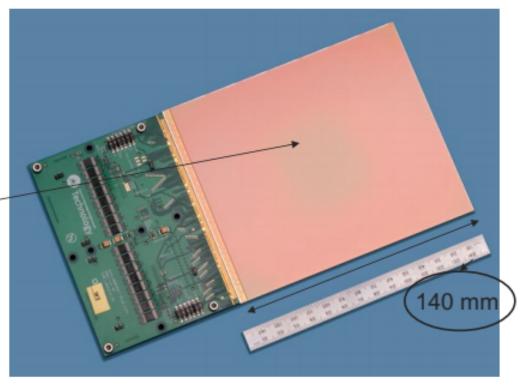

#### Detector Modules with ALPIDE Chips

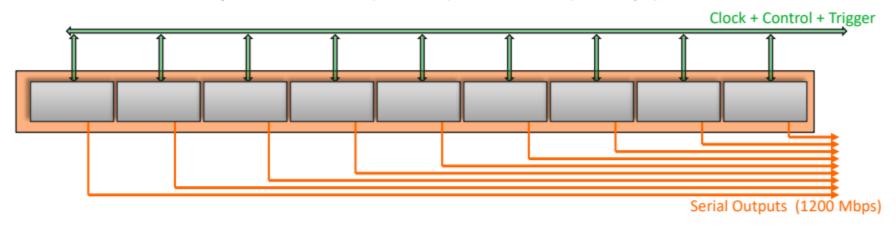

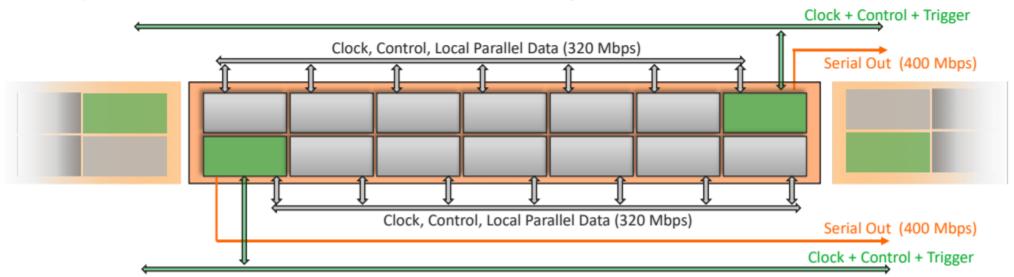

ITS Inner Barrel Module – 9 chips, shared clock (40 MHz) and control (40 Mbps), individual data readout lines

ITS Outer Barrel Module – 2 groups of chips, Master + 6 Slaves

Only the Master interfaces to the external world and bridges control and data transfer

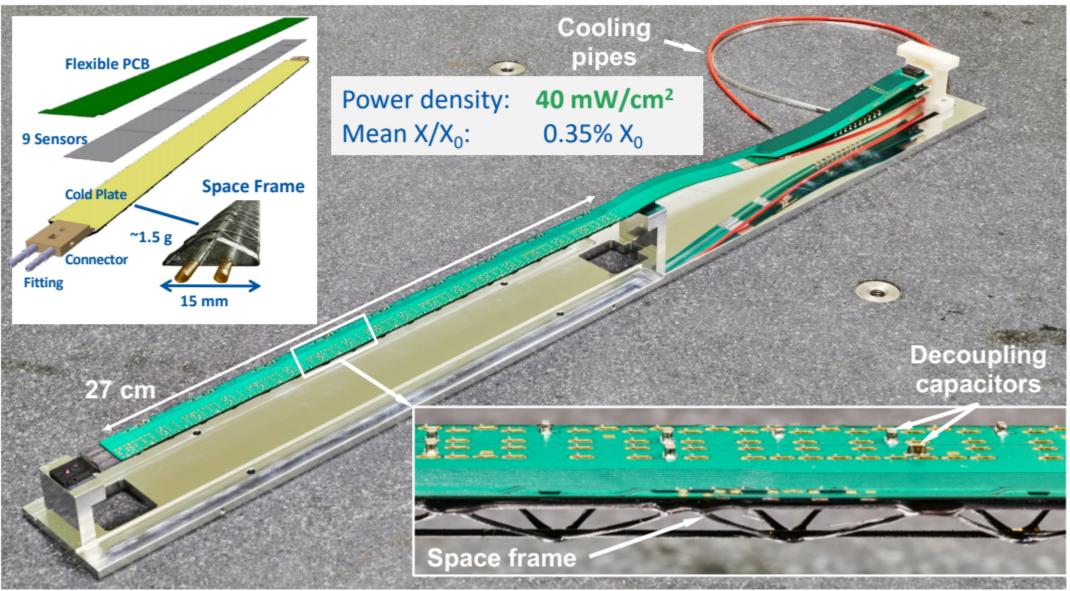

#### **Inner Barrel Stave**

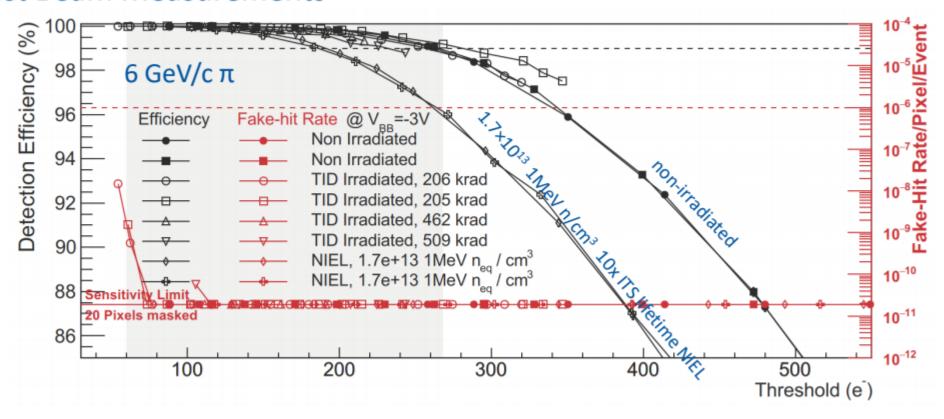

## Detection Efficiency and Fake Hit Rate

#### **Test Beam Measurements**

Large operational margin with O(10) masked pixels (0.002%)

Fake hit rate < 2\*10<sup>-11</sup> pixel hits/event

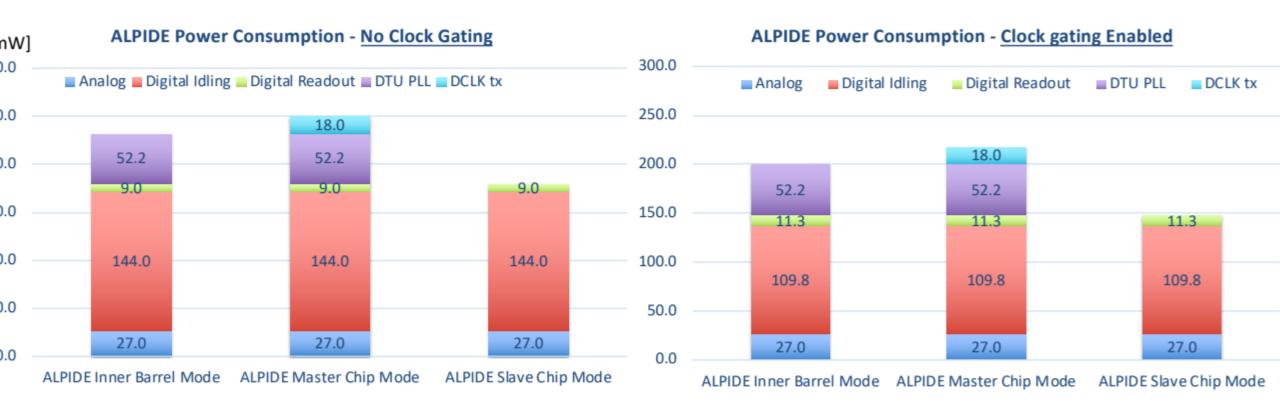

#### **Typical Power Consumption Figures**

**Clock Gating OFF**

Inner Barrel Mode: 51 mW/cm<sup>2</sup>

Outer Barrel Average: 42 mW/cm2

**Clock Gating ON**

Inner Barrel Mode: 44 mW/cm<sup>2</sup>

Outer Barrel Average: 35 mW/cm2

# ITS3 & The next steps

# MAPS (Monolithic Active Pixel Sensors) for Imaging and More

Many developments in the field of CMOS imaging sensors and MAPS in general within the community!

Example:

Wafers scale (8") imaging sensor developed by the RAL team (stitched)

N. Guerrini, RAL, 5th school on detectors, Legnaro, April 2013

# TJ 180 nm modified process

- Novel modified process developed in collaboration of CERN with TJ foundry in context of ALICE ITS.

- Combined with a small collection diode.

- Adding a planar n-type layer significantly improves depletion under deep PWELL

- Increased depletion volume → fast charge collection by drift

- better time resolution reduced probability of charge trapping (radiation hardness)

- Possibility to fully deplete sensing volume with no significant circuit or layout changes

#### **ALPIDE-REBIN**

What we deal with is the digital storage, and all modification is in periphery.

# Towards timing device: 50 ( $\mu$ )-thick Si sensor under usual condition

Assuming Si sensor thickness  $50\mu$  and  $\vec{E} = \frac{20 V}{50 \mu}$ , carrier drift time will be

$$v_e \sim 5.6 \cdot 10^6 \left(\frac{cm}{s}\right)$$

$\Delta t_{50 \,\mu} \sim 0.9 \cdot 10^{-9} \,(s)$

Generic time resolution for sensor will be good!

Contents lists available at ScienceDirect

Nuclear Inst. and Methods in Physics Research, A

journal homepage: www.elsevier.com/locate/nima

W. Snoeys a,\*, G. Aglieri Rinella A, H. Hillemanns A, T. Kugathasan A, M. Mager L. Musa A, P. Riedler a, F. Reidt J. Van Hoorne A, A. Fenigstein , T. Leitner

a CERN, CH-1211 Geneva 23, Switzerland

b TowerJazz Semiconductor, Migdal Haemek, 23105, Israel